POWER DEVICES AND SYSTEMS LABORATORY

# Exercise 7<sup>A</sup>

## Design and Prototyping of a Switched-Mode Power Converter

Indicatory work plan

| Week  | Class in the Laboratory                                                                                                     | Own Work at Home                                               | Teacher's Office Hours                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------|

| 11–12 | Assignment of individual parameters                                                                                         | Board design (Task 1)                                          | Consultation                                 |

| 12-13 | Consultation                                                                                                                | Power supply design or<br>analysis<br>(Tasks 2 and 3–6 or 7–9) | Consultation<br>Board design approval *      |

| 13    | Delivery and assembly of pre-<br>defined components                                                                         | Controller design<br>(Tasks 10–12)                             | Consultation<br>Electronic design approval * |

| 14    | 14Delivery and assembly of<br>calculated componentsAssembly verification<br>Transistor selection<br>verification (Tasks 13- |                                                                |                                              |

| 15    | Start-up, measurements **<br>Operation approval                                                                             | Report completion                                              | Consultation<br>Report approval              |

\* Ultimate deadline. Solutions must be presented to the teacher beforehand so that there is time available for necessary modifications still before this deadline.

\*\* Tasks described in Manual 7<sup>C</sup>.

## Exercise and manual elaborated by: Łukasz Starzak

Łódź 2016

## Contents

| Α  | Cours | se Introduction                                                | 7  |

|----|-------|----------------------------------------------------------------|----|

| 1. | Prin  | ted Prototype Circuit Boards                                   | 7  |

|    | 1.1.  | Universal Printed Circuit Boards                               |    |

|    |       | 1.1.a. Board structure                                         |    |

|    |       | 1.1.b. Circuit design                                          |    |

|    | 1.2.  | Using the worksheet and design example                         |    |

|    |       | 1.2.a. Design support worksheet                                |    |

|    |       | 1.2.b. Circuit for the design example                          |    |

|    |       | 1.2.c. Preparation for design                                  |    |

|    |       | 1.2.d. Component placement and connection planning             |    |

|    |       | 1.2.e. Design verification and improvement                     |    |

| В  | Exerc | ise Introduction                                               | 21 |

| 2. | Exer  | cise Aim and Plan                                              | 21 |

|    |       | What do we aim at? Design goals                                |    |

|    |       | By what means will we achieve it? Exercise outline             |    |

| 3. | DC (  | Chopper                                                        | 25 |

|    | 3.1.  | Circuit idea                                                   | 25 |

|    |       | 3.1.a. Principle of operation                                  |    |

|    |       | 3.1.b. Power conversion characteristics                        |    |

|    | 3.2.  | Practical circuit                                              |    |

|    |       | 3.2.a. Adaptation to design requirements                       |    |

|    |       | 3.2.b. Practical circuit operation                             |    |

|    |       | 3.2.c. Detailed schematic and functional blocks                |    |

|    |       | 3.2.d. Conditioning and protection devices                     |    |

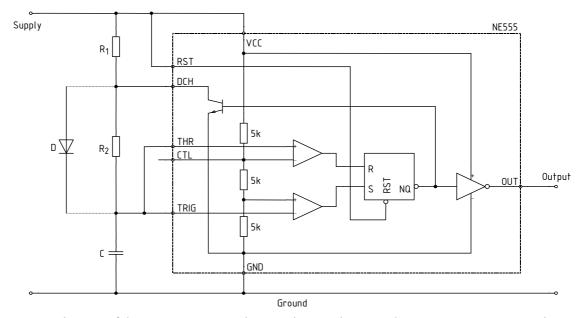

|    | 3.3.  | Pulse wave generator                                           |    |

|    |       | 3.3.a. Basic astable configuration                             |    |

|    |       | 3.3.b. Modified astable configuration                          |    |

|    |       | 3.3.c. Application circuit                                     |    |

|    |       | 3.3.d. Current consumption                                     |    |

| С  | Desig | n                                                              | 39 |

| 4. | PCB   | Design                                                         |    |

|    | 4.1.  | General Assumptions                                            | 39 |

|    |       | 4.1.a. Electrical schematic of the board                       |    |

|    |       | 4.1.b. Universal PCB used                                      |    |

|    | 4.2.  | The real electrical character of connections                   |    |

|    |       | 4.2.a. Effect of physical connections on circuit operation     |    |

|    |       | 4.2.b. Schematic representation                                |    |

|    |       | 4.2.c. Specific requirements for connections                   |    |

|    | 4.3.  | Realisation                                                    |    |

|    |       | Task 1. Component placement and connection planning on the PCB | 57 |

| 5. | Elec  | tronic Design                                                  |    |

|    | 5.1.  | Introductory notes and calculations                            |    |

|    |       | Guidelines for task accomplishment                             |    |

|    |       | Task 2. Circuit characteristic values, upper estimate          |    |

|    | 5.2.  | Power supply component selection                               |    |

|    |       | Task 3*. Short-circuit protection                              |    |

|    |       | Task 4*. Rectifier filter                                      |    |

|    |       | Task 5*. Controller supply voltage                             |    |

|    |       | Task 6*. Controller power supply filter                        |    |

© 2016 Łukasz Starzak, Katedra Mikroelektroniki i Technik Informatycznych Politechniki Łódzkiej

|    | 5.3.  | Power supply operation                                    | 68 |

|----|-------|-----------------------------------------------------------|----|

|    |       | Task 7**. Controller supply voltage: maximum estimation   |    |

|    |       | Task 8**. Rectified voltage: minimum amplitude estimation |    |

|    |       | Task 9**. Controller supply voltage: minimum estimation   |    |

|    | 5.4.  | Controller                                                | 72 |

|    |       | Task 10. Pulse wave generator: calculations               |    |

|    |       | Task 11. Pulse wave generator verification   74           |    |

|    |       | Task 12. Transistor's gate circuit76                      |    |

|    | 5.5.  | Semiconductor switch selection verification               | 78 |

|    |       | Task 13. Transistor voltage rating79                      |    |

|    |       | Task 14. Transistor power loss 80                         |    |

|    |       | Task 15. Transistor thermal safety                        |    |

|    |       | Task 16**. Control circuit operating conditions           |    |

|    |       |                                                           |    |

| ΕI | ntorn | nation                                                    | 85 |

| 6. | Exer  | cise Realisation Rules                                    | 85 |

| 7. | Expe  | cted Report Contents                                      | 86 |

| 8. | Requ  | iired Knowledge                                           | 87 |

|    | 8.1.  | Prerequisites                                             | 87 |

|    | 8.2.  | Test scope                                                | 87 |

| 9. | Refer | rences                                                    | 87 |

## Figures

| Fig. 1. Single sided universal PCB with pre-connected solder pads                            | 8  |

|----------------------------------------------------------------------------------------------|----|

| Fig. 2. Schematic of the circuit used in the design example                                  |    |

| Fig. 3. Board and components for the design example                                          |    |

| Fig. 4. Solder pads and pre-manufactured connections image defined in the spreadsheet Płytka |    |

| Fig. 5. Board design process                                                                 | 14 |

| Fig. 6. The example circuit assembled and operating                                          |    |

| Fig. 7. Final image of the universal board obtained in the design example                    |    |

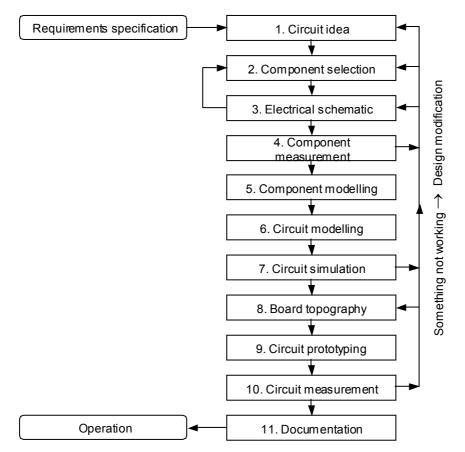

| Fig. 8. Work path of a circuit design and prototyping engineer                               | 22 |

| Fig. 9. General schematic of the DC chopper with a resistive receiver                        | 25 |

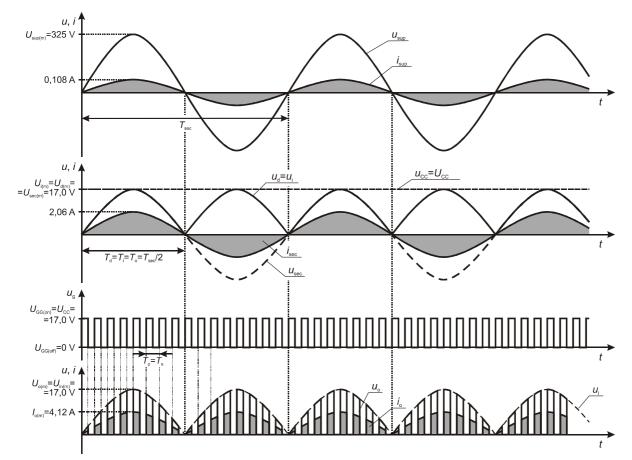

| Fig. 10. Current and voltage waveforms in the DC chopper circuit for exemplary input voltage | e  |

| waveform and duty cycle                                                                      | 26 |

| Fig. 11. The initial halogen lamp circuit                                                    | 29 |

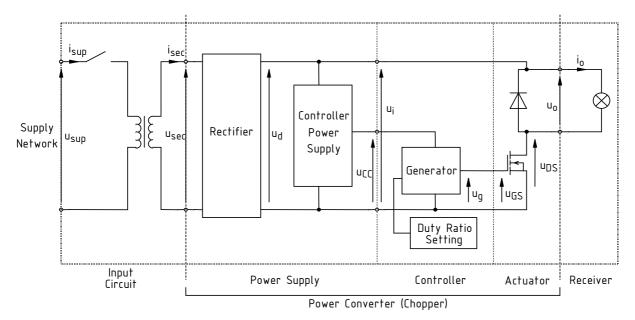

| Fig. 12. Block diagram of a complete lamp dimmer circuit based on a DC chopper               | 30 |

| Fig. 13. Simplified waveforms in an ideal DC chopper circuit (Fig. 12)                       | 30 |

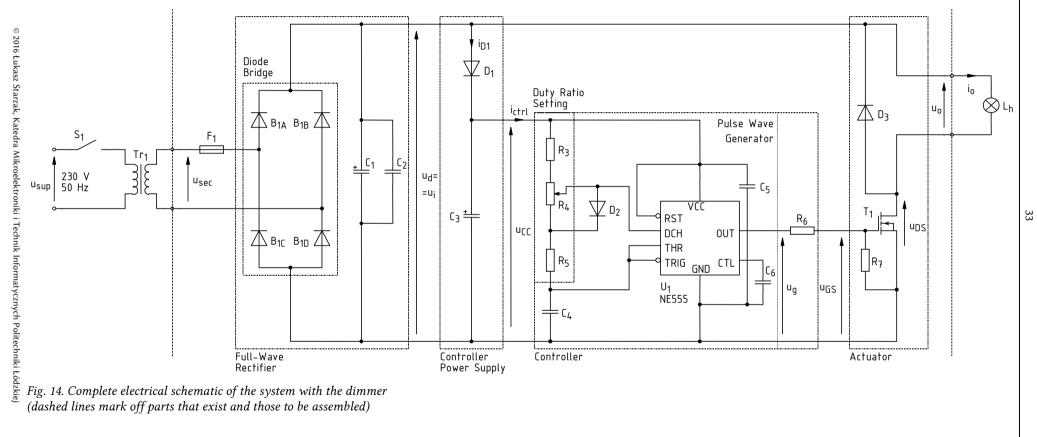

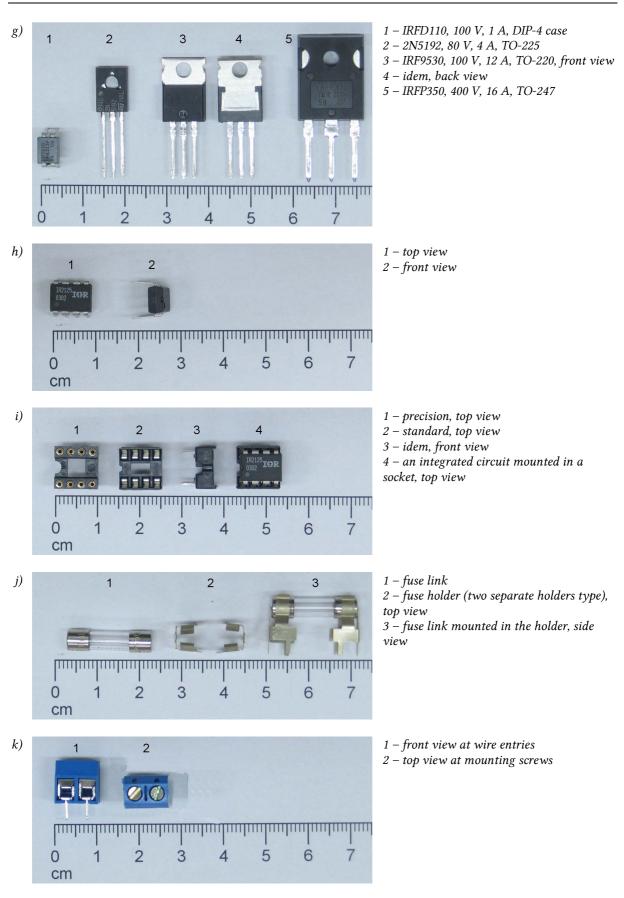

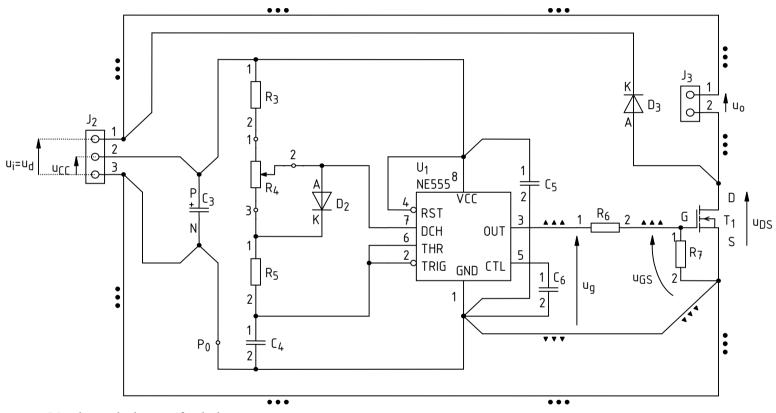

| Fig. 14. Complete electrical schematic of the system with the dimmer                         | 33 |

| Fig. 15. Schematic of the 555 timer integrated circuit showing the external component        |    |

| connections with the optional diode                                                          | 35 |

| Fig. 16. A simplified image of conducting trace and solder pads layout for the UM-8 board    | 40 |

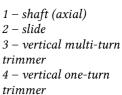

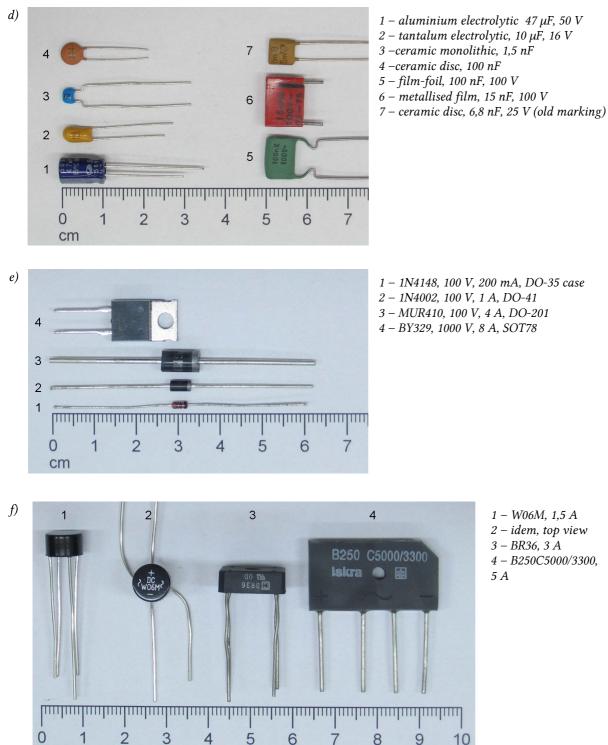

| Fig. 17. Electronic components                                                               | 41 |

| Fig. 18. PCB electrical schematic for the full option                                        |    |

| Fig. 19. PCB electrical schematic for the basic option                                       | 45 |

## Tables

| Table 1. Lead arrangement and case outline for the components used in the design example | 12 |

|------------------------------------------------------------------------------------------|----|

| Table 2. Design parameters                                                               | 23 |

| Table 3. Component list                                                                  |    |

| Table 4. Additional circuit component data                                               |    |

| Table in Haddinenal encour compensation                                                  |    |

# A

## **Course Introduction**

## 1. Printed Prototype Circuit Boards

## 1.1. Universal Printed Circuit Boards

## 1.1.a. Board structure

For prototyping the physical circuit, a *universal prototyping printed circuit board* (*universal PCB*) may be used. It is a flat piece of laminate (a plastic made of two different materials), 1 to 2 mm thick, with pre-drilled (frequently at equal distances) *mounting holes* and pre-manufactured (usually one-sided) *solder pads* (the metallisation surrounding the hole, enabling to solder a component's lead or a conductor). Mounting holes are frequently pre-connected with regularly placed metallic *conducting traces*.

As such a board may be used to prototype an arbitrary circuit, it is called 'universal.' Universal PCBs are frequently used for circuit prototyping to avoid the time-consuming PCB design, etching and drilling where it is very likely for the circuit idea still to change multiple times.

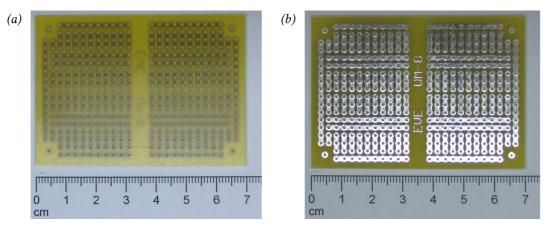

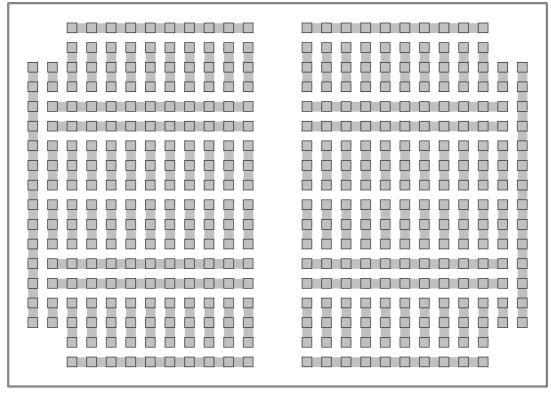

Fig. 1 presents a view of an exemplary universal prototype PCB. It is a *single sided* PCB, i.e. with metallic traces manufactured on its one side only (which makes it different from the *double sided* PCBs), where solder pads have been pre-connected. This board has a *lead pitch* of 2.5 mm which means that holes and pads (where component leads may be soldered) are placed at the nodes of a 2.5-millimeter square grid.

Trace layout is similar on most universal PCBs. Multiple short vertical connections are manufactured (the vertical and horizontal directions obviously being conventional). Above and below them, longer horizontal traces are realised that are commonly used to distribute power supply and ground to the particular components. Such traces may also be placed vertically, sparsely distributed in the interior or along board edges (the latter being the case of Fig. 1). A board with such a trace layout is well suited for the present exercise.

A universal PCB may be partitioned into several separate sub-circuits. For example, on the board presented in the photograph, 2 separated sub-circuits can be seen (in its left-hand and right-hand sides). Moreover, each of the sub-circuits has two separate connection rows along two horizontal double middle lines (in the upper and lower board quarter). For these rows, only the long vertical trace along the board edge is common.

*Fig. 1. Single sided universal PCB with pre-connected solder pads (a) component side; (b) solder side*

As already mentioned, a PCB that has metallisation realised only on its one side is called a single sided PCB. The side on which connections have been manufactured is called the *solder side* whereas the other is the *component side*. Components are essentially placed on the component side (although this is not always the case, especially when a component has to be added). Soldering is done on the solder side.

In the present exercise, the circuit will be realised using the *through-hole technique* (or *through-hole mount*). This term means that component leads are passed through mounting holes to the solder side where they are soldered to solder pads. This technique is very well suited for circuit prototyping because of high soldering speed and the lack of high precision and special care requirements.

However, in final product manufacturing, the *surface-mount technique* (SMT) became more widespread. Sometimes it is necessary or easier to use *surface-mount devices* (components in SMT-dedicated casings, SMD) already at the prototyping stage. For this purpose, special universal PCBs are manufactured that enable soldering an SMD and providing one or more mounting holes per each of its pins. Using these holes and the through-hole technique, a complete circuit prototype can be assembled. Such boards usually do not have metal traces except for those connecting device pins with corresponding mounting holes.

## 1.1.b. Circuit design

As the universal PCB used in this exercise has a pre-manufactured trace layout, circuit design activities are limited to:

- 1) planning the device placement,

- 2) determining if and where additional connections are needed.

Action 2 is usually necessary as a universal PCB obviously is 'universal' only to some extent. Before starting the PCB design. The additional connections are realised in one of the following ways:

- with an ordinary insulated conductor—usually on the component side; both connector ends are passed through mounting holes and soldered to the solder pads just as device leads are;

- 2) with a bare wire, e.g. dedicated silvered copper wire or simply a component lead fragment cut off—usually on the device side (if on the solder side, it is necessary to ensure that the wire does not cause unwanted shorts along its length, also when incidentally deformed); wire mounting is done as previously;

- 3) with solder on the solder side (only possible when neighbouring traces are to be connected)—in this case solder pads are usually not occupied;

- 4) with a longer lead of an element connected to the same voltage as the points being connected (only possible if such a lead exists), bent on the solder side in line with the designed connection— this is a more reliable and easier alternative

to technique 3 as the laminate is often covered with a solder resist layer counteracting solder connecting neighbouring pads.

During universal PCB design the following rules are usually applied.

- 1. The design process is started with integrated circuit sockets. They are placed in dedicated areas, e.g. in the case of the board shown in Fig. 1 pins would be placed apart at both sides of the double horizontal traces. On larger boards, integrated circuits are usually placed in the middle.

- 2. Integrated circuits impose particular long traces to be chosen as supply and ground. Usually, supply and ground pins are top left and top right, or top left and bottom left, or top left and bottom right ones—this must be checked in the data sheet. It is desirable that a maximum number of devices are directly connected to a supply (or ground) trace.

- 3. If the PCB has special solder pads for specific connectors, placement begins with these connectors and then integrated circuits connected to them are placed.

- 4. After the integrated circuits, other devices are placed. One should start with those devices that are closest (in the electrical schematic or according to functional requirements) to the integrated circuits. De-coupling capacitors are placed first.

- 5. When placing passive elements, the designer should take advantage of the possibility of shorting or—the opposite—leaving long device leads. Vertical mount and appropriate shorting of the leads of an axial case enables inserting them even in neighbouring holes. On the other hand, making use of their full (or slightly shortened) length may eliminate the need for additional connections.

- 6. It should be kept in mind that device cases have determinate geometrical dimensions. They may cover up and make inaccessible some neighbouring mounting holes. This especially concerns electrolytic capacitors, coils, larger diodes and transistors, diode bridges, buttons, potentiometers and connectors.

- 7. Device terminals that are mutually connected in the electrical schematic should be placed on one conducting trace. Only when this is impossible, an additional connection is made.

- 8. Two solder pads should be provided for each additional connection. When neighbouring traces are to be connected, this may be done using solder itself (and possibly an additional supporting wire) on the solder side, without occupying any mounting holes, as described above.

- 9. No loops should be created together with the additional connections, i.e. moving along traces and additional connections in a chosen direction, we should never get back to the starting point. Loops will behave as antennas, emitting and intercepting electro-magnetic disturbances which may cause improper circuit operation.

- 10. If coils are present in the circuit (not the case of the present exercise), it should be avoided to place them in the vicinity of integrated circuits or above traces connected to any other devices.

- 11. Power loops (high-voltage or high-current ones) should have the shortest perimeter and the lowest area enclosed possible. Their elements should therefore be placed the closest possible one to another.

- 12. Additional connections in high-current loops are realised using high-crosssection wires. Due to the low diameter of mounting holes, it may be necessary to solder these wires on the solder side.

- 13. Also the leads of high-current devices may have a diameter larger than the diameter of mounting holes. This should be checked on the board design stage (in device data sheets) or after devices are collected (empirically) but *before* circuit assembly starts. Too tight holes will have to be broadened using a drill, taking special care not to damage the solder pads and adjacent traces.

- 14. Device placement is usually finalised with connectors and potentiometers, which must be put in easily accessible points. These frequently are the board edges. Connection paths to the rest of the circuit should be the shortest possible and should involve the least possible number of additional connections.

- 15. In the case of prototypes, additional horizontal shorts, vertical measurement pins or measurement points (small loops) are mounted on the board. There are intended to enable attaching oscilloscope probes to the key circuit nodes during testing.

## 1.2. Using the worksheet and design example

#### 1.2.a. Design support worksheet

In order to limit the number of errors and to ease design verification, you should use the worksheet *plytka\_uniwersalna.ods* if designing with the prototype board. A general description of this worksheet is available as an attachment to this manual.

Now we will follow an exemplary design based on a universal PCB. Let's assume that the circuit shown in Fig. 2 has to be assembled and that the universal prototyping board already presented in Fig. 1 is to be used.

#### 1.2.b. Circuit for the design example

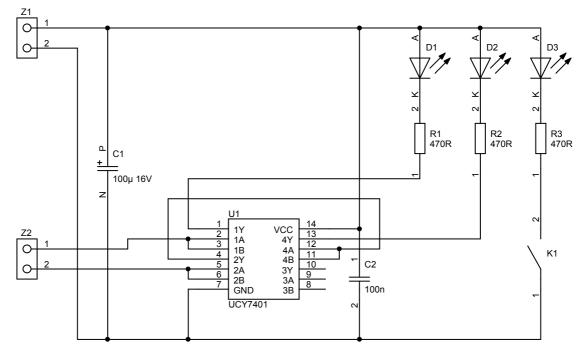

The exemplary circuit has a supply input through the  $Z_1$  connector (a terminal block) and a double signal input through the  $Z_2$  connector. The supply is stabilised with the  $C_1$  electrolytic capacitor. High-frequency disturbances are carried off to the ground through the  $C_2$  de-coupling ceramic capacitor.

The  $U_1$  integrated circuit includes 4 NAND gates numbered from 1 to 4 whose inputs are labelled as A and B, and outputs as Y. The VCC pin is the supply positive potential and the GND pin is the supply ground. These gates are used as buffers for signals 1 and 2 that come from some outputs with too low a current capability to make the Light Emitting Diodes (LEDs) light up. In the case of the signal 1 it is an inverting buffer as a single NAND gate with shorted inputs acts as a NOT gate. For the signal 2 it is a non-inverting buffer as two such NOT gates are connected in cascade.

Gate outputs are supplied from a voltage connected to the VCC and GND pins, so from the source connected to the circuit through the  $Z_1$  connector. We assume that current capability of this source is sufficient to light up the LEDs. Setting a given Y output in the logical zero state, i.e. the low level, means electrically connecting this output to the GND pin, so the ground. In the case of 1Y and 4Y outputs this will close a loop starting from  $Z_1$  connector's terminal 1 and ending at its terminal 2: through  $D_1$  and  $R_1$  or through  $D_2$  and  $R_2$  components. This will enable current flow and lighting up the corresponding LED.

Fig. 2. Schematic of the circuit used in the design example

The third LED  $(D_3)$  is supplied directly and turns on when the K<sub>1</sub> button is pushed (or the key is closed). The 3 resistors R<sub>1</sub>, R<sub>2</sub> and R<sub>3</sub> enable setting the diode current value, which is equal to the supply voltage decreased by the voltage drop across the diode and divided by the resistor's value.

## 1.2.c. Preparation for design

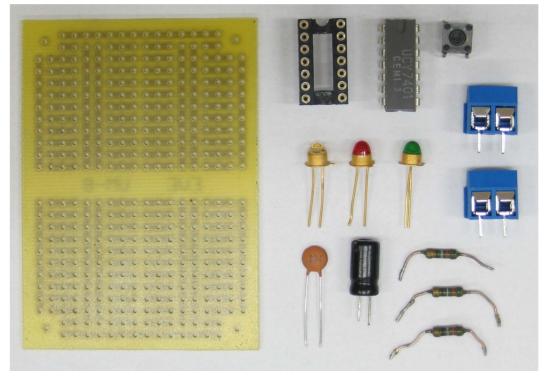

In order to start the design, it is necessary to know the lead arrangement and spacing for the particular components as well as their case dimensions (precisely, the dimensions of case projection onto the board surface). Together with professional PCB design software, case outline libraries are delivered. In our case, outlines and lead arrangement are shown in Table 1 against the solder pads grid of the board to be used (so, a single distance between holes is 2.5 mm).

The universal board together with all the components are pictured in Fig. 3.

| Component                             | Integrated circuit, DIP-14                                         | Miniature button                                |

|---------------------------------------|--------------------------------------------------------------------|-------------------------------------------------|

| Case outline with lead<br>arrangement | .14       .13       .12       .11       .10       .9       .8      | .1#1#                                           |

| Component                             | Terminal block, 2-pole, RM 5                                       | Electrolytic capacitor, vertical,<br>Ø6, RM 2,5 |

| Case outline with lead<br>arrangement | z tej strony wejście przewodów<br>Wires enter from the bottom side | I.N .P                                          |

| Component                             | Light Emitting Diode                                               | Capacitor, ceramic disc                         |

| Case outline with lead<br>arrangement |                                                                    | .1 .2                                           |

| Component                             | Resistor, 1/4 W, horizontal mount                                  | Resistor, 1/4 W, vertical mount                 |

| Case outline with lead<br>arrangement | .1 .2                                                              | .1 2                                            |

Table 1. Lead arrangement and case outline for the components used in the design example (terminal labels are consistent with Fig. 2)

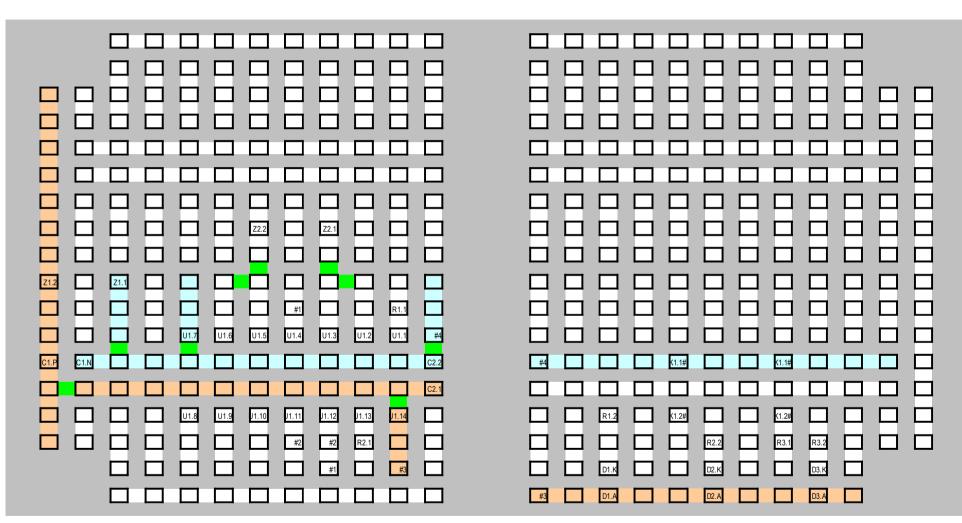

Design begins with the entry of the solder pads and connecting traces image to the spreadsheet *Plytka*, the effect being presented in Fig. 4. Grey represents the laminate surface, white represents metallic paths (traces) and black frames represent solder pads (so, mounting holes as well).

Into the spreadsheet *Węzły schematu* data about electrical connections in the circuit according to Fig. 2 are introduced. The considered circuit has 11 electrical nodes which results in the below circuit description.

C1.P U1.14 C2.1 Z1.1 D1.A D2.A D3.A Z1.2 C1.N U1.7 C2.2 K1.1 Z2.1 U1.2 U1.3 Z2.2 U1.5 U1.6 U1.4 U1.11 U1.12 U1.1 R1.1

| R1.2  | D1.K |

|-------|------|

| U1.13 | R2.1 |

| R2.2  | D2.K |

| K1.2  | R3.1 |

| R3.2  | D3.K |

Fig. 3. Board and components for the design example

Fig. 4. Solder pads and pre-manufactured connections image defined in the spreadsheet Płytka

## 1.2.d. Component placement and connection planning

We are now beginning the design process proper.

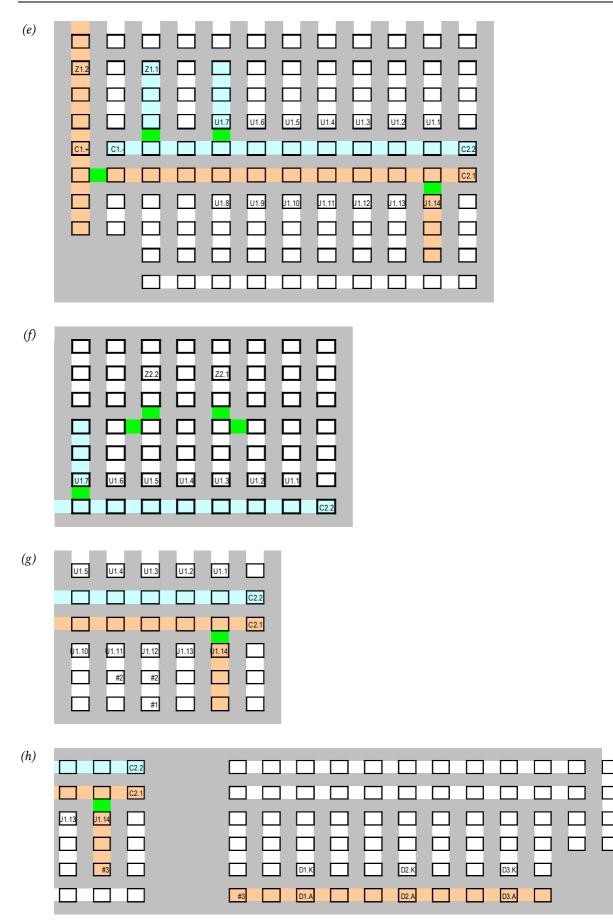

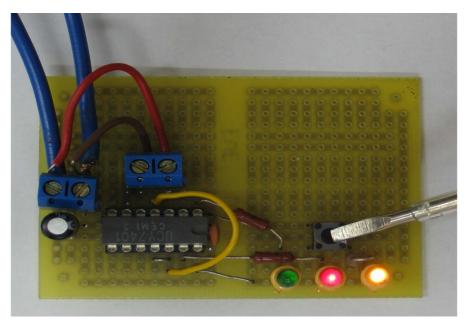

We start with the U<sub>1</sub> integrated circuit (see Section 1.1.b, pt 1. We will place it along one of the long horizontal traces. As it has two input signals connected from the left-hand side (in the schematic) and the Z<sub>1</sub> terminal block has fairly large dimensions, we decide to locate the IC in the bottom left quarter of the board, so that there is enough space for the terminal block above it (on the board). On the other hand, right of the IC (on the board) we leave free space for the C<sub>2</sub> de-coupling capacitor. The result is shown in Fig. 5(a).

| (a)     | Image: state stat |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| (b)     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| (c)     | U1.3       U1.2       U1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| (d)     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Fig. 5. | $\begin{array}{c} z_{2} \\ \hline \\ 0 \\ z \\ z$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Fig. 5. Board design process

Fig. 5 (cont.) Board design process

| (i) | Image: selection of the se |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| (j) | R1.1       #4         U1.1       #4         C22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Image: select | Image: state stat |  |

| (k) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

2. The IC imposes specific long horizontal traces to be chosen as supply (the one neighbouring the pin 14 or VCC, see Section 1.1.b, pt 2) and as ground (the one neighbouring the pin 7 or GND). We mark them with pink and cyan and connect to the appropriate pins of the  $U_1$  integrated

circuit using solder on the solder side (a wire can be avoided as neighbouring traces are being connected, see Section 1.1.b, pt 8), which we mark with green. The result is shown in Fig. 5(b).

- 3. The  $C_2$  de-coupling capacitor is inserted between the supply and ground traces, the closest possible to the supply pin (VCC) of the U<sub>1</sub> IC (see Section 1.1.b, pt 4), taking care to connect terminal 2 to the ground and terminal 1 to the supply. Otherwise, the automated design check will fail because the board will be incompatible with the schematic. The result is presented in Fig. 5(c).

- 4. On the left end of the supply traces there is enough space for connecting the supply (the  $Z_1$  terminal block) and the  $C_1$  blocking capacitor. It is best to insert the capacitor directly into the traces as there will so be no need for any additional connections; in this case, we will place the terminal block above the capacitor. The supply path has therefore to be bent to the top (towards the terminal block), for which purpose we use the long vertical trace along the board's edge. The ground trace will be bent along the shorter path. We plan to make all the necessary connections using solder on the solder side. We update supply and ground path colouring and check whether they do not form a loop (see Section 1.1.b, pt 9).

If the terminal block was to be inserted according to the schematic, i.e. with the ground connected to Z1.2, the front of this block would have to face the  $C_1$  capacitor, which would impede inserting wires (see Section 1.1.b, pt 14). We therefore insert it with its *back* facing the capacitor which forces us to modify the electrical schematic by connecting the ground to Z1.1 and the supply to Z1.2 [see Fig. 5(d) where a circle shows the modified part). The final result is presented in Fig. 5(e).

- 5. Now we can place the  $Z_2$  terminal block, however, making sure to leave enough space between it and the IC to make the connections going out from pins 1 and 4. We can notice that it will be profitable to locate the Z2.1 pin just opposite the U1.3 pin, and Z2.2 opposite U1.5 because such connections are present in the electrical schematic. We short the pins as appropriate, U1.2 with U1.3 and U1.5 with U1.6, using solder as they are placed on neighbouring traces. The result is presented in Fig. 5(f).

- 6. We make last connections in the vicinity of the IC: U1.4 with U1.12 using a wire that we label #1 and U1.12 with U1.11 using a wire that we label #2. The result is presented in Fig. 5(g).

- 7. Only diodes and resistors are left for placement now (except for the K<sub>1</sub> button that we will keep aside until the location of R<sub>3</sub> and D<sub>3</sub> components connected with it is determined). As all the three anodes must be at the supply potential, we will connect them to one of the long traces (see Section 1.1.b, pt 7). We choose the one running along the edge of the bottom right quarter of the board because it is located relatively close to the IC and there is enough space above it for the three resistors and the button. The supply is brought to this trace from pin 14 of the IC using the wire #3. We should keep in mind that according to the table, each diode occupies about 3 solder pad distances (see Section 1.1.b, pt 6). The result is presented in Fig. 5(h).

- 8. The leads of  $R_1$  and  $R_2$  resistors are originally longer than the minimum lengths shown in Table 1. We can take advantage of this to make direct connections between the cathodes of  $D_1$  and  $D_2$  and the corresponding outputs of the IC, without using any additional wires (see Section 1.1.b, pt 5). We must only try to avoid their crossing with other components or provide an appropriate (vertical) distance between them, or protect the leads with insulating tubes. The result is presented in Fig. 5(i).

- 9. On the contrary, the R<sub>3</sub> resistor will be mounted vertically, to fit the K<sub>1</sub> button just beside. The button will be placed in such a way that its other end is inserted into the long horizontal line. We continue along this line to the left, to a point nearest the existing ground trace, and we insert the wire #4 for the missing part of the connection. Due to the closest solder pad being occupied by the C2.2 terminal, we insert the other end of the wire do the neighbouring, free pad and connect to the ground trace using the solder.

Attention should be paid to terminate the labels of the  $K_1$  button's terminals with the hash sign "#" as they are shorted in pairs inside the component. In order for this to be taken into account during design check, both terminals of a pair must be given the same label which moreover must end with a hash sign (see the worksheet description attached).

10. Component placement is finished. The result is presented in Fig. 5(k).

## 1.2.e. Design verification and improvement

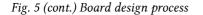

11. We will now check the correctness of our design using the macro *\_SprawdzPolaczenia*. Verification causes an error message to be displayed telling us about discrepancy in connections between the schematic and the board:

In the 3<sup>rd</sup> line of such a message, terminals connected to a same node in the schematic are listed. In the 5<sup>th</sup> line, terminals connected to the same node on the board are listed. We can state that there are 3 differences between these lists:

- there is a C1.- terminal on the board which, according to the schematic, should be labelled C1.N; on this occasion, C1.+ should obviously be also changed to C1.P;

- 2) the K1.1 terminal is not present in the board-based list which means we have not connected it to the ground; indeed, we have mistakenly placed the second end of the wire #4, opposite the first one instead of one solder pad below; we move it to the proper location;

- 3) the trace corresponding to the displayed list connects to Z1.1 while based on the schematic it appears that it should connect to Z1.2; in this case, this is the sheet *Węzły schematu* that is wrong as we forgot to update it after the connections of the Z<sub>1</sub> connector were exchanged.

After correcting, the schematic is described as follows:

```

Z1.1 C1.N U1.7 C2.2 K1.1

Z1.2 C1.P U1.14 C2.1 D1.A D2.A D3.A

Z2.1 U1.2 U1.3

Z2.2 U1.5 U1.6

U1.4 U1.11 U1.12

U1.1 R1.1

R1.2 D1.K

U1.13 R2.1

R2.2 D2.K

K1.2 R3.1

R3.2 D3.K

```

while the new image of the board is presented in Fig. 7.

12. We launch the check again. This time the error concerns the following terminals:

| Schemat: | U1.11 U1.12 U1.4 |

|----------|------------------|

| Płytka:  | U1.10            |

where Schemat lists the terminals in the schematic and Plytka lists the terminals on the board.

We check the unconnected U1.10 terminal which appears in the board-based list and we state that it indeed should be floating. The same applies to U1.9 and U1.8. Unfortunately, we did not allow for it in the node list. We must therefore introduce three additional nodes to the sheet *Węzły schematu*, with only one terminal assigned to each of them. Sheet contents are now as follows:

Z1.1 C1.N U1.7 C2.2 K1.1

Z1.2 C1.P U1.14 C2.1 D1.A D2.A D3.A

Z2.1 U1.2 U1.3

Z2.2 U1.5 U1.6

U1.4 U1.11 U1.12

© 2016 Łukasz Starzak, Katedra Mikroelektroniki i Technik Informatycznych Politechniki Łódzkiej

- U1.1 R1.1 R1.2 D1.K U1.13 R2.1 R2.2 D2.K K1.2 R3.1 R3.2 D3.K U1.8 U1.9 U1.10

- 13. We launch the check again. There is no error now which means that the connections planned on the board are consistent with those described in the sheet *Węzły schematu* that reflects the electrical schematic.

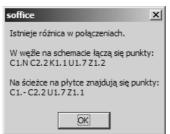

Fig. 6 shows the circuit assembled according to Fig. 7 and operating. The original circuit may be inspected in the laboratory room as is also the case of an exemplary dimmer as designed in the present exercise.

Fig. 6. The example circuit assembled and operating

*Fig. 7. Final image of the universal board obtained in the design example*

## **Exercise Introduction**

## 2. Exercise Aim and Plan

## What is this exercise for? Circuit realisation on an engineer's work path

The aim of the present exercise is to get acquainted with the most basic issues of prototyping switched mode power electronic circuits. A MOSFET will be used as the controllable semiconductor switch. This exercise is therefore a direct continuation of Exercises 3 and 6, thus filling the gap in the engineer's work path presented in Fig. 8.

During this exercise realisation, you will learn basics of control circuit design for power semiconductor devices based on the principle of variable pulse width. Additionally, you will get acquainted with universal PCB circuit design rules, electronic circuits assembly and the procedures of their starting up and testing.

The present exercise is an occasion to sum up your work of the whole semester. This manual will therefore be referring to knowledge and information from previous exercises. This includes the following problems:

- control of switched mode power electronic circuits through varying the pulse width of the semiconductor switch control signal

- item 1 (in Fig. 8) > Ex.  $3^{B}$ ,  $4^{B}$ ;

- semiconductor device selection considering the requirements imposed by the circuit

- item 2  $\succ$  Ex. 1, 5<sup>A</sup>, 5<sup>B</sup>, 6<sup>A</sup>;

- specifics of controlled semiconductor switches operation with real loads item  $3 \ge \text{Ex. 6}^{\text{B}}$ ;

- driving field-effect power semiconductor devices – item  $3 \ge \text{Ex. } 3^{\text{A}}, 3^{\text{B}};$

- static parameters measurement of semiconductor devices

item 4 ➤ Ex. 5<sup>A</sup>;

- static parameters measurement of semiconductor devices

item 4 ≥ Ex. 3<sup>A</sup>, 4<sup>A</sup>;

- semiconductor device modelling for thermal calculations

item 5 ➤ Ex. 6<sup>A</sup>, 6<sup>B</sup>;

- − electronic circuit modelling and simulation – items 6 and 7  $\geq$  Ex. 6<sup>A</sup>;

- measurements of voltages, currents and power in electronic circuits using an oscilloscope, a voltage probe, a current probe, a digital multimeter

item 10 ≥ Ex. 2, 3, 4, 5<sup>B</sup>, 6<sup>B</sup>;

- work documentation

- item 11 ➤ all exercises.

Fig. 8. Work path of a circuit design and prototyping engineer

Exercise 7 will complement the above knowledge and skills in respect of:

- circuit prototype design using a universal PCB: item 8;

- electronic circuit assembly using the though-hole mount technique: item 9.

This manual concerns circuit design, covering items 1 to 8 in the above presented schematic. A next part of the exercise will be devoted to assembly, start-up, operation tests and characteristics measurements (items 9 to 10). The documentation will be created on an ongoing basis.

## What do we aim at? Design goals

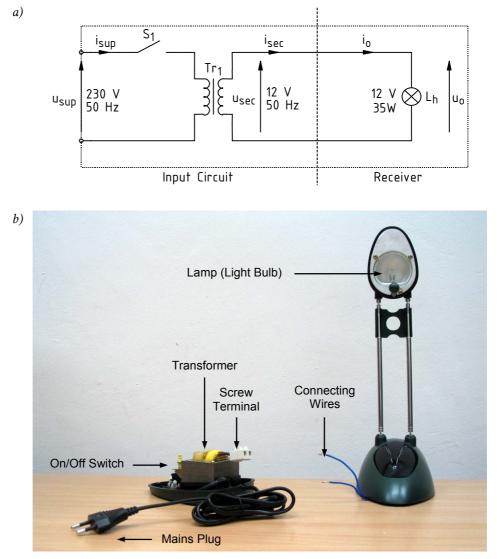

You should design and prototype a possibly simple dimmer for a halogen lamp desk light with a nominal power of 35 W and a nominal voltage of 12 V, operating in the switched mode and based on the pulse width regulation technique. Some design parameters are set for each team individually. These are included in a table that will be handed over by the teacher.

The original circuit is supplied from the 230 V, 50 Hz mains through a 230 V / 12 V transformer. The dimmer should be inserted between the transformer's secondary winding and the lamp using

wires. Easy connection and disconnection of transformer and lamp-side wires should be ensured. The potentiometer used to adjust light intensity should not be soldered to the PCB directly but connected on wires.

Design parameters have been gathered in Table 2.

| Tuble 2. Design parameters                                         |                        |              |

|--------------------------------------------------------------------|------------------------|--------------|

| Dimmer input voltage rms value                                     | Usec                   | 12 V         |

| Dimmer input voltage frequency                                     | $f_{ m sec}$           | 50 Hz        |

| (Rms) nominal voltage of the halogen<br>lamp                       | U <sub>Lh(nom)</sub>   | 12 V         |

| Nominal average power of the halogen lamp                          | P <sub>Lh(nom)</sub>   | 35 W         |

| Dimmer switching frequency                                         | $f_{\rm s}$            | (560) kHz *  |

| Minimum duty cycle                                                 | $D_{\min}$             | 0,100,20 *   |

| Maximum duty cycle                                                 | D <sub>max</sub>       | 0,850,95 *   |

| Maximum average current drawn by the generator's auxiliary circuit | I <sub>R3(av)max</sub> | (530) mA *   |

| Semiconductor switch                                               | T <sub>1</sub>         | MOSFET *     |

| Rise time for the semiconductor switch                             | tr                     | (50150) ns * |

Table 2. Design parameters

\* Specific data are contained in the attachment handed over by the teacher.

## By what means will we achieve it? Exercise outline

The present exercise may be carried out in one of the following two options:

- full option it comprises the *Supply* and *Control* blocks in Fig. 12 and results in a complete, ready for independent operation, circuit being assembled; there are 22 elements to be arranged and soldered;

- (2) **basic option** it comprises the *Control* block in Fig. 12 only and therefore the assembled circuit will need an additional *Supply* block, which is available in the laboratory; there are 15 elements to be arranged and soldered.

Choosing the basic option does not influence exercise evaluation negatively. In principle, the full option is meant for people who already have some experience in assembling electronic circuits and consider that the basic option does not fulfil their ambition, or for people that are motivated to gain new skills (the teachers will provide any help needed).

The exercise is carried out according to the following outline:

- 1. Board design (device arrangement on a universal prototyping PCB or own PCB design): Chapter 4

- 2. Electronic design (element values selection in chosen functional blocks) with verification through simulation: Chapter 5

- 3. Circuit prototyping (may be started as soon as the board design is ready but finished only after electronic design is completed)

- 4. Setting the circuit working and testing for correct operation: Manual  $7^{\circ}$

- 5. Measurements of chosen characteristics of the assembled circuit: Manual 7<sup>C</sup>

Carrying out of this exercise must be documented with a report through <u>manually filling in the</u> <u>form</u> that is attached to this manual.

Specific rules for carrying out this exercise are presented in Chapter 6, p. 85.

## 3. DC Chopper

## 3.1. Circuit idea

#### 3.1.a. Principle of operation

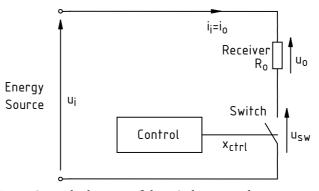

The schematic of the circuit that has been chosen to obtain the dimmer functionality has been presented in Fig 9. It is called a *DC chopper* which reflects the essence of its operation very well. The input voltage  $u_i$  may be constant but also variable with a low frequency  $f_i$  and a corresponding period  $T_i$ . It still is a DC power converter as long as most of the average power is connected with the DC components of voltage and current.

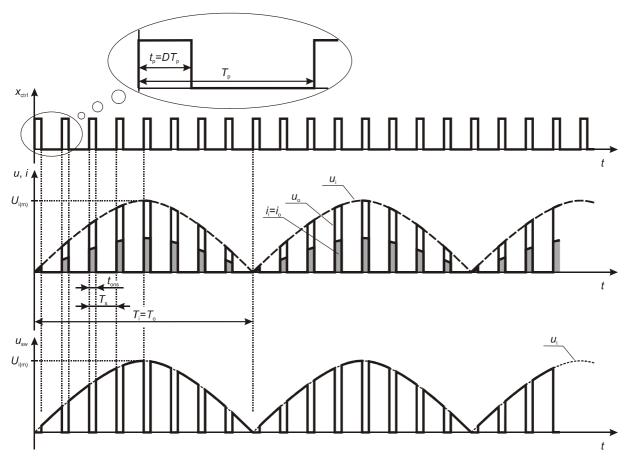

It follows from the schematic that the input voltage is applied across the receiver (the output voltage  $u_0$  with a same period  $T_0 = T_i$ ). However, it is not applied directly but *chopped* as the switch periodically, with a frequency  $f_s$  higher than the possible input frequency  $f_i$ , interrupts the application of the input voltage. Waveforms observed in the circuit of Fig. 9, under the assumption that all its components are ideal and that the load is stationary and resistive (of some equivalent resistance  $R_0$ ) is presented in Fig. 10. When the key is closed,  $u_0 = u_i$ , and when it is open,  $u_0 = 0$ .

*Fig. 9. General schematic of the DC chopper with a resistive receiver*

The ratio of the pulse width  $t_p$  of the quantity  $x_{ctrl}$  controlling the switch to the pulse repetition period  $T_p$  is the parameter called the **duty cycle** > Exercises 3<sup>B</sup>, 6. As a result of application of this control signal, the switch is turned on and off with a switching period  $T_s$  (which obviously equals  $T_p$ ). If we assume that the switch is ideal, i.e. switching times are zero, then the switch on-state time  $t_{ons}$  equals the pulse width  $t_p$ . Thus

*Fig. 10. Current and voltage waveforms in the DC chopper circuit for exemplary input voltage waveform and duty cycle*

$$D = \frac{t_{\rm p}}{T_{\rm p}} \approx \frac{t_{\rm ons}}{T_{\rm s}} \tag{3.1}$$

The operation of the considered circuit is described by two important terms:  $\succ$  Exercises 2, 3<sup>B</sup>

- switched-mode circuit which refers to the semiconductor switch being alternatingly turned on and off with a high frequency (as compared to input waveforms, output waveforms or to various time constants present in this circuit);

- 2) *pulse width modulation* which is the method for obtaining a desired output (current, voltage, power, ...; instantaneous, rms, average, ...) by changing the duty cycle of the pulse waveform controlling the semiconductor switch.

## 3.1.b. Power conversion characteristics

From the rms value definition, the rms output voltage is given by

$$U_{\rm o(rms)} \stackrel{\Delta}{=} \sqrt{\frac{1}{T_{\rm o}} \int_{T_{\rm o}} u_{\rm o}^2 dt}$$

(3.2)

where  $T_0$  is the  $u_0$  waveform period. It follows from the circuit topology (Fig. 9) and the analysis done in Section 3.1.a that the output voltage period  $T_0$  equals that of the input voltage  $T_i$ . Interrupting the applied to the receiver means making it zero for a given period of time (the switch's off-state duration). Therefore, the rms value of  $u_0$  is lowered when the duty cycle *D* is decreased

because the integral decreases  $\geq$  Exercise 2. It may be shown that this is quantitatively described by the formula

$$U_{\rm o(rms)} \approx \sqrt{D} \cdot U_{\rm o(rms)max} = \sqrt{D} \cdot U_{\rm i(rms)}$$

(3.3)

where  $U_{o(rms)max}$  is the maximum rms output voltage that can be obtained. As can be seen, it is obtained for D = 1, so without any chopper action, the input voltage being constantly applied to the receiver without any interruption. Therefore, for D = 1,  $u_0 = u_i$  and

$$U_{o(rms)max} = U_{o(rms)}\Big|_{D=1} = U_{i(rms)}$$

(3.4)

which is already reflected in Eq. (3.3).

For a resistive receiver, the average output power is

$$P_{\rm o} = \frac{U_{\rm o(rms)}^2}{R_{\rm o}} \tag{3.5}$$

Substituting (3.3) into the above, we obtain

$$P_{\rm o} = \frac{U_{\rm o(rms)}^2}{R_{\rm o}} \approx \frac{DU_{\rm i(rms)}^2}{R_{\rm o}} = DP_{\rm o,max}$$

(3.6)

where  $P_{o,max}$  is the maximum average output power, which is obtained for D = 1 and amounts

$$P_{\rm o,max} = P_{\rm o}\Big|_{D=1} = \frac{U_{\rm i(rms)}^2}{R_{\rm o}} = \frac{U_{\rm o(rms)max}^2}{R_{\rm o}}$$

(3.7)

Taking into account that the load is resistive, we can also derive how the load current varies, based on the Ohm's law:

$$I_{\rm o(rms)} = \frac{U_{\rm o(rms)}}{R_{\rm o}} = \sqrt{D} \frac{U_{\rm o(rms)max}}{R_{\rm o}} = \sqrt{D} \frac{U_{\rm i(rms)}}{R_{\rm o}} = \sqrt{D} \cdot I_{\rm o(rms)max}$$

(3.8)

where, as can be seen, the maximum rms output current, obtained for D = 1, is

$$I_{o(rms)max} = I_{o(rms)}\Big|_{D=1} = \frac{U_{o(rms)max}}{R_o} = \frac{U_{i(rms)}}{R_o}$$

(3.9)

## 3.2. Practical circuit

#### 3.2.a. Adaptation to design requirements

The DC chopper has been chosen to solve the technical problem stated in Chapter 2 because of its simplicity. As we will see in this section, it is just a low-side switch, appropriately supplied and controlled  $\geq$  Exercises 3, 4, 6.

The desired function could obviously be realised more efficiently by some more complex circuits (DC choppers, DC converters etc.) On the other hand, there are even less complex solutions such as some AC voltage controllers  $\geq$  Exercise 2. The DC chopper, however, presents several qualities typical for pulse width modulated circuits such as the possibility of obtaining a higher power factor  $\geq$  Exercise 2.