# CPU32

## REFERENCE MANUAL

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

MOTOROLA and eregistered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### **PREFACE**

This reference manual describes programming and operation of the CPU32 instruction processing module, found in the M68300 Family of embedded controllers. It is part of a multivolume set of manuals — each volume corresponds to a major module in the M68300 Family.

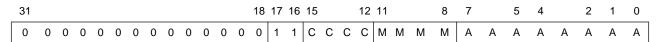

A user's manual for each device incorporating the CPU32 describes processor function and operation with reference to other modules within the device.

This manual consists of the following sections and appendix:

Section 1 Overview

Section 2 Architecture Summary

Section 3 Data Organization and Addressing Capabilities

Section 4 Instruction Set

Section 5 Processing States

Section 6 Exception Processing

Section 7 Development Support

Section 8 Instruction Execution Timing

Appendix A M68000 Family Summary

Index

#### NOTE

In this manual, the terms assertion and negation specifya particular logic state. **Assert** and **assertion** refer to an active or true signal. **Negate** and **negation** refer to an inactive or false signal. These terms are used independently of the voltage level that they represent.

This manual is written for systems designers, systems programmers, and applications programmers. Systems designers need general knowledge of the entire volume, with particular emphasis on Section 1, Section 7, and Appendix A — they will also need to be familiar with electrical specifications and mechanical data contained in the user's manual. Systems programmers should become familiar with Sections 1 through 6, Section 8, and Appendix A. Applications programmers can find most of the information they need in Sections 1 through 5, Section 8, and Appendix A.

This manual is also written for users of the M68000 Family that are not familiar with the CPU32. Although there are comparative references to other Motorola microprocessors throughout the manual, Section 1, Section 2, and Appendix A specifically identify the CPU32 within the M68000 Family, and discuss the differences between it and related devices.

## **TABLE OF CONTENTS**

| Paragra | aph Title                                                 | Page |

|---------|-----------------------------------------------------------|------|

|         |                                                           |      |

|         | SECTION 1 OVERVIEW                                        |      |

| 1.1     | Features                                                  | 1-1  |

| 1.1.1   | Virtual Memory                                            | 1-2  |

| 1.1.2   | Loop Mode Instruction Execution                           | 1-2  |

| 1.1.3   | Vector Base Register                                      |      |

| 1.1.4   | Exception Handling                                        | 1-3  |

| 1.1.5   | Enhanced Addressing Modes                                 | 1-4  |

| 1.1.6   | Instruction Set                                           |      |

| 1.1.6.1 | Table Lookup and Interpolation Instructions               | 1-4  |

| 1.1.6.2 | Low-Power Stop Instruction                                | 1-6  |

| 1.1.7   | Processing States                                         |      |

| 1.1.8   | Privilege States                                          | 1-6  |

| 1.2     | Block Diagram                                             |      |

|         | SECTION 2ARCHITECTURE SUMMARY                             |      |

|         | SECTION ZARCHITECTURE SUMMART                             |      |

| 2.1     | Programming Model                                         | 2-1  |

| 2.2     | Registers                                                 | 2-2  |

| 2.3     | Data Types                                                | 2-3  |

| 2.3.1   | Organization in Registers                                 | 2-4  |

| 2.3.1.1 | Data Registers                                            | 2-4  |

| 2.3.1.2 | Address Registers                                         | 2-5  |

| 2.3.1.3 | Control Registers                                         | 2-5  |

| 2.3.2   | Organization in Memory                                    | 2-6  |

| 8       | SECTION 3 DATA ORGANIZATION AND ADDRESSING CAPABILITIES   |      |

| 3.1     | Program and Data References                               | 3-1  |

| 3.2     | <b>G</b>                                                  | 3-2  |

| 3.3     | Implicit Reference                                        | 3-2  |

| 3.4     | Effective Address                                         |      |

| 3.4.1   | Register Direct Mode                                      | 3-3  |

| 3.4.1.1 | Data Register Direct                                      |      |

| 3.4.1.2 | Address Register Direct                                   |      |

| 3.4.2   | Memory Addressing Modes                                   |      |

| 3.4.2.1 | Address Register Indirect                                 |      |

| 3.4.2.2 | Address Register Indirect With Postincrement              | 3-4  |

| 3.4.2.3 | Address Register Indirect With Predecrement               |      |

| 3.4.2.4 | Address Register Indirect With Displacement               |      |

| 3.4.2.5 | Address Register Indirect With Index (8-Bit Displacement) | 3-5  |

| 3.4.2.6 | Address Register Indirect With Index (Base Displacement)  | 3-6  |

|         |                                                           |      |

CPU32

| Paragra        | aph Title                                                 | Page                    |

|----------------|-----------------------------------------------------------|-------------------------|

| 3.4.3          | Special Addressing Modes                                  | 3_7                     |

| 3.4.3.1        | Program Counter Indirect With Displacement                |                         |

| 3.4.3.2        | Program Counter Indirect with Index (8-Bit Displacement)  |                         |

| 3.4.3.3        | Program Counter Indirect with Index (8 Base Displacement) |                         |

| 3.4.3.4        | Absolute Short Address                                    |                         |

| 3.4.3.5        | Absolute Long Address                                     |                         |

| 3.4.3.6        | Immediate Data                                            |                         |

| 3.4.4          | Effective Address Encoding Summary                        |                         |

| 3.5            | Programming View of Addressing Modes                      |                         |

| 3.5.1          | Addressing Capabilities                                   |                         |

| 3.5.2          | General Addressing Mode Summary                           | 3-14                    |

| 3.6            | M68000 Family Addressing Capability                       | 3-14                    |

| 3.7            | Other Data Structures                                     |                         |

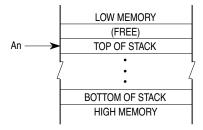

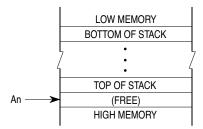

| 3.7.1          | System Stack                                              |                         |

| 3.7.2          | User Stacks                                               |                         |

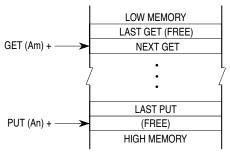

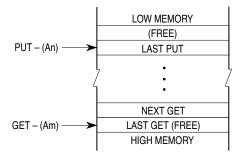

| 3.7.3          | Queues                                                    | 3-17                    |

|                | SECTION 4 INSTRUCTION SET                                 |                         |

| 4.1            | M68000 Family Compatibility                               | 4-1                     |

| 4.1.1          | New Instructions                                          |                         |

| 4.1.1.1        | Low-Power Stop (LPSTOP)                                   | 4-1                     |

| 4.1.1.2        | Table Lookup and Interpolation (TBL)                      | 4-2                     |

| 4.1.2          | Unimplemented Instructions                                |                         |

| 4.2            | Instruction Format                                        |                         |

| 4.2.1          | Notation                                                  |                         |

| 4.3            | Instruction Summary                                       |                         |

| 4.3.1          | Condition Code Register                                   |                         |

| 4.3.2          | Data Movement Instructions                                |                         |

| 4.3.3<br>4.3.4 | Integer Arithmetic OperationsLogic Instructions           |                         |

| 4.3.4          | Shift and Rotate Instructions                             |                         |

| 4.3.6          | Bit Manipulation Instructions                             |                         |

| 4.3.7          | Binary-Coded Decimal (BCD) Instructions                   | <del>4</del> -9<br>⊿₌1∩ |

| 4.3.8          | Program Control Instructions                              |                         |

| 4.3.9          | System Control Instructions                               |                         |

| 4.3.10         | Condition Tests                                           |                         |

| 4.4            | Instruction Details                                       |                         |

| 4.5            | Instruction Format Summary4                               |                         |

| 4.6            | Table Lookup and Interpolation Instructions4              |                         |

| 4.6.1          | Table Example 1: Standard Usage4                          |                         |

| 4.6.2          | Table Example 2: Compressed Table4                        |                         |

| Paragra                                                                                                      | aph Title                                                                                                                                                                                                                                                                                               | Page                                          |

|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 4.6.3<br>4.6.4<br>4.6.5                                                                                      | Table Example 3: 8-Bit Independent Variable  Table Example 4: Maintaining Precision  Table Example 5: Surface Interpolations                                                                                                                                                                            | 4-192<br>4-194                                |

| 4.7<br>4.8                                                                                                   | Nested Subroutine Calls  Pipeline Synchronization with the NOP Instruction                                                                                                                                                                                                                              |                                               |

|                                                                                                              | SECTION 5PROCESSING STATES                                                                                                                                                                                                                                                                              |                                               |

| 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.3<br>5.3.1<br>5.3.1.1<br>5.3.1.2<br>5.3.1.3<br>5.3.1.4<br>5.3.1.5 | State Transitions Privilege Levels Supervisor Privilege Level User Privilege Level Changing Privilege Level Types of Address Space CPU Space Access Type 0000 — Breakpoint Type 0001 — MMU Access Type 0010 — Coprocessor Access Type 0011 — Internal Register Access Type 1111 — Interrupt Acknowledge | 5-1<br>5-2<br>5-2<br>5-3<br>5-3<br>5-4<br>5-4 |

|                                                                                                              | SECTION 6 EXCEPTION PROCESSING                                                                                                                                                                                                                                                                          |                                               |

| 6.1<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5                                                             | Definition of Exception Processing                                                                                                                                                                                                                                                                      | 6-1<br>6-2<br>6-3<br>6-3                      |

| 6.2<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>6.2.5<br>6.2.6<br>6.2.7                                           | Processing of Specific Exceptions  Reset  Bus Error  Address Error  Instruction Traps  Software Breakpoints  Hardware Breakpoints  Format Error                                                                                                                                                         | 6-5<br>6-5<br>6-6<br>6-7<br>6-8<br>6-8        |

| 6.2.8<br>6.2.9<br>6.2.10<br>6.2.11<br>6.2.12                                                                 | Illegal or Unimplemented Instructions Privilege Violations Tracing Interrupts Return from Exception                                                                                                                                                                                                     | 6-9<br>6-10<br>6-11                           |

| Paragra | aph Title                                              | Page |

|---------|--------------------------------------------------------|------|

| 6.3     | Fault Recovery                                         | 6-14 |

| 6.3.1   | Types of Faults                                        |      |

| 6.3.1.1 | Type I: Released Write Faults                          |      |

| 6.3.1.2 | Type II: Prefetch, Operand, RMW, and MOVEP Faults.     |      |

| 6.3.1.3 | Type III: Faults During MOVEM Operand Transfer         |      |

| 6.3.1.4 | Type IV: Faults During Exception Processing            |      |

| 6.3.2   | Correcting a Fault                                     |      |

| 6.3.2.1 | (Type I) Completing Released Writes via Software       | 6-19 |

| 6.3.2.2 | (Type I) Completing Released Writes via RTE            |      |

| 6.3.2.3 | (Type II) Correcting Faults via RTE                    |      |

| 6.3.2.4 | (Type III) Correcting Faults via Software              | 6-20 |

| 6.3.2.5 | (Type III) Correcting Faults By Conversion and Restart | 6-20 |

| 6.3.2.6 | (Type III) Correcting Faults via RTE                   | 6-21 |

| 6.3.2.7 | (Type IV) Correcting Faults via Software               | 6-21 |

| 6.4     | CPU32 Stack Frames                                     |      |

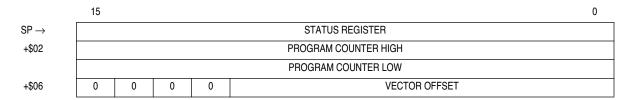

| 6.4.1   | Normal Four-Word Stack Frame                           | 6-22 |

| 6.4.2   | Normal Six-Word Stack Frame                            | 6-22 |

| 6.4.3   | BERR Stack Frame                                       | 6-22 |

|         | SECTION 7 DEVELOPMENT SUPPORT                          |      |

| 7.1     | CPU32 Integrated Development Support                   |      |

| 7.1.1   | Background Debug Mode (BDM) Overview                   |      |

| 7.1.2   | Deterministic Opcode Tracking Overview                 |      |

| 7.1.3   | On-Chip Hardware Breakpoint Overview                   |      |

| 7.2     | Background Debug Mode (BDM)                            |      |

| 7.2.1   | Enabling BDM                                           |      |

| 7.2.2   | BDM Sources                                            |      |

| 7.2.2.1 | External BKPT Signal                                   |      |

| 7.2.2.2 | BGND Instruction                                       |      |

| 7.2.2.3 | Double Bus Fault                                       |      |

| 7.2.2.4 | Peripheral Breakpoints                                 |      |

| 7.2.3   | Entering BDM                                           | 7-5  |

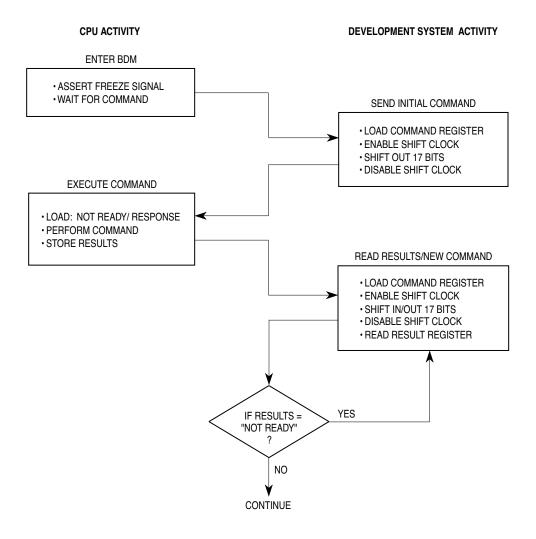

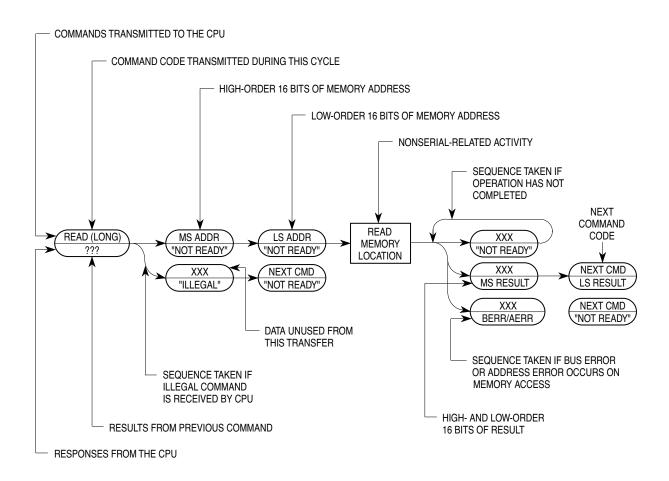

| 7.2.4   | Command Execution                                      |      |

| 7.2.5   | Background Mode Registers                              | 7-6  |

| 7.2.5.1 | Fault Address Register (FAR)                           | 7-6  |

| 7.2.5.2 | Return Program Counter (RPC)                           |      |

| 7.2.5.3 | Current Instruction Program Counter (PCC)              |      |

| 7.2.6   | Returning from BDM                                     |      |

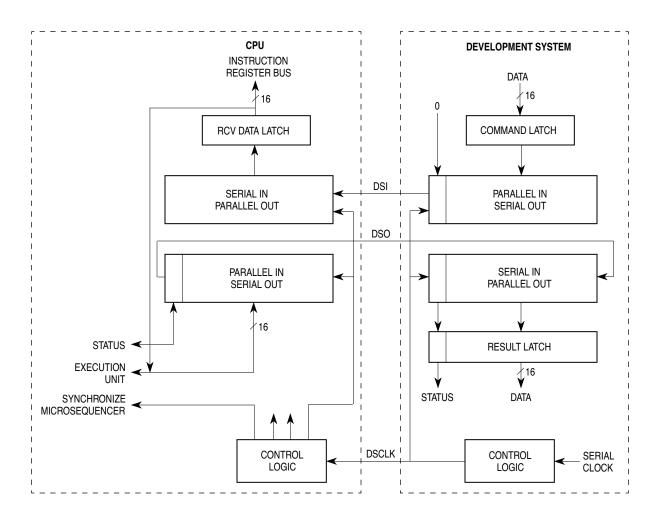

| 7.2.7   | Serial Interface                                       |      |

| 7.2.7.1 | CPU Serial Logic                                       |      |

| 7.2.7.2 | Development System Serial Logic                        | /-10 |

| Paragra            | ipn little                                                | Page  |

|--------------------|-----------------------------------------------------------|-------|

| 700                | Command Cat                                               | 7 4 4 |

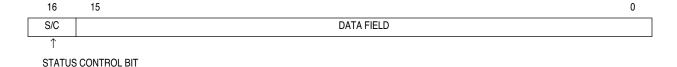

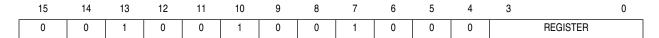

| 7.2.8<br>7.2.8.1   | Command Set  Command Format                               |       |

| _                  |                                                           |       |

| 7.2.8.2            | Command Set Summan                                        |       |

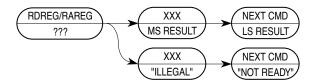

| 7.2.8.3            | Command Set SummaryRead A/D Register (RAREG/RDREG)        |       |

| 7.2.8.4            |                                                           |       |

| 7.2.8.5<br>7.2.8.6 | Write A/D Register (WAREG/WDREG)                          |       |

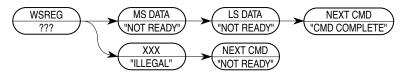

| 7.2.8.7            | Read System Register (RSREG)                              |       |

| 7.2.8.8            | Write System Register (WSREG)                             |       |

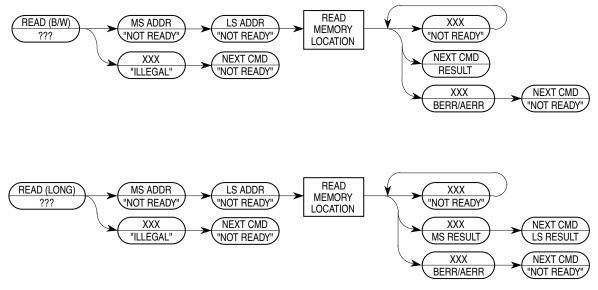

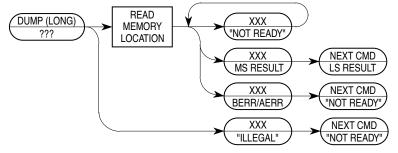

| 7.2.8.9            | Read Memory Location (READ)                               |       |

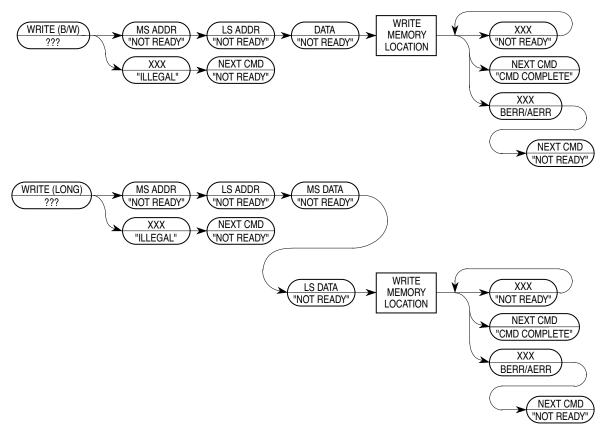

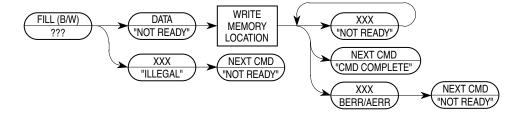

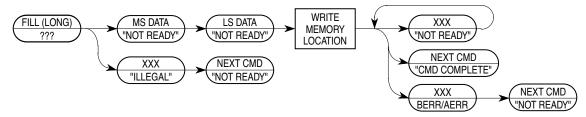

| 7.2.8.10           | Write Memory Location (WRITE)                             |       |

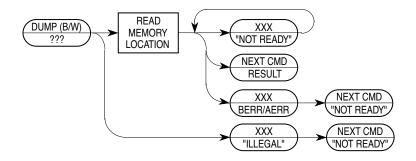

| 7.2.8.10           | , , ,                                                     |       |

| 7.2.8.11           | / /                                                       |       |

| 7.2.8.12           | ` '                                                       |       |

| 7.2.8.14           | ,                                                         |       |

| 7.2.8.14           | • ,                                                       |       |

| 7.2.8.16           | . ,                                                       |       |

| 7.2.6.10           | Deterministic Opcode Tracking                             |       |

| 7.3<br>7.3.1       | , ,                                                       |       |

| 7.3.1              | Instruction Fetch (IFETCH)                                |       |

| 7.3.2<br>7.3.3     | Instruction Pipe (IPIPE) Opcode Tracking during Loop Mode |       |

| 1.3.3              | Opcode Tracking during Loop Mode                          | 1-21  |

|                    | SECTION 8 INSTRUCTION EXECUTION TIMING                    |       |

| 8.1                | Resource Scheduling                                       | 8-1   |

| 8.1.1              | Microsequencer                                            | 8-1   |

| 8.1.2              | Instruction Pipeline                                      | 8-2   |

| 8.1.3              | Bus Controller Resources                                  | 8-2   |

| 8.1.3.1            | Prefetch Controller                                       | 8-3   |

| 8.1.3.2            | Write-Pending Buffer                                      |       |

| 8.1.3.3            | Microbus Controller                                       | 8-3   |

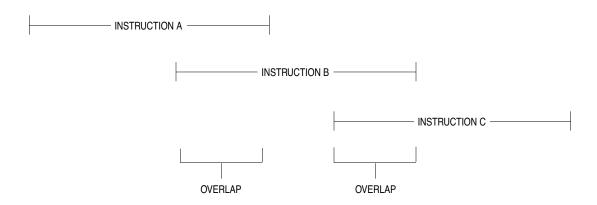

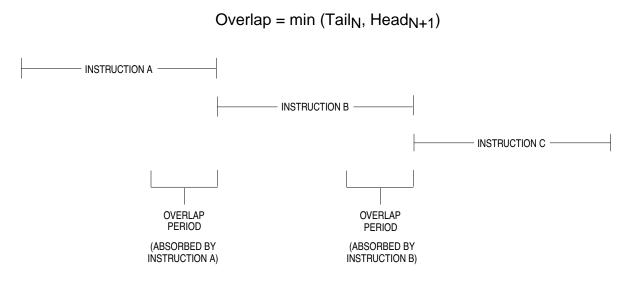

| 8.1.4              | Instruction Execution Overlap                             | 8-4   |

| 8.1.5              | Effects of Wait States                                    |       |

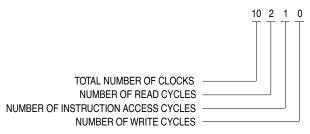

| 8.1.6              | Instruction Execution Time Calculation                    | 8-5   |

| 8.1.7              | Effects of Negative Tails                                 |       |

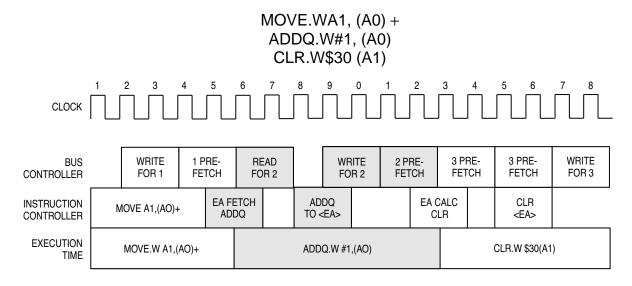

| 8.2                | Instruction Stream Timing Examples                        | 8-7   |

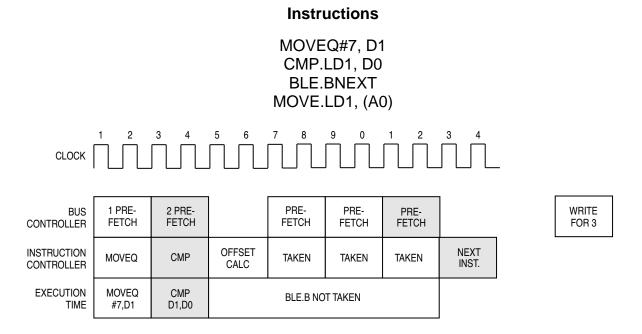

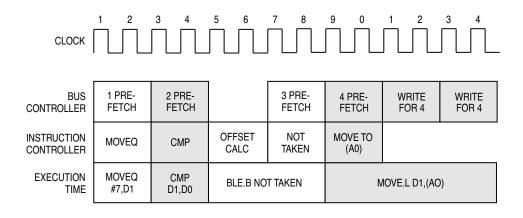

| 8.2.1              | Timing Example 1: Execution Overlap                       |       |

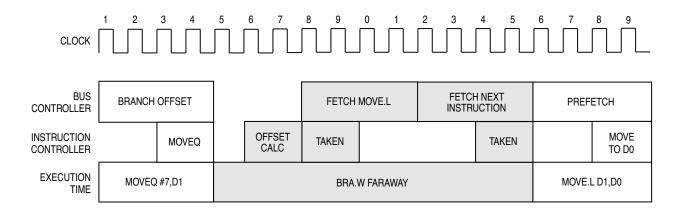

| 8.2.2              | Timing Example 2: Branch Instructions                     | 8-8   |

| 8.2.3              | Timing Example 3: Negative Tails                          | 8-9   |

| 8.3                | Instruction Timing Tables                                 | 8-10  |

| 8.3.1              | Fetch Effective Address                                   |       |

| 8.3.2              | Calculate Effective Address                               | 8-13  |

| Paragraph | Litle                                          | Page |

|-----------|------------------------------------------------|------|

| 8.3.3     | MOVE Instruction                               | 8-14 |

| 8.3.4     | Special-Purpose MOVE Instruction               | 8-14 |

| 8.3.5     | Arithmetic/Logic Instructions                  | 8-15 |

| 8.3.6     | Immediate Arithmetic/Logic Instructions        | 8-17 |

| 8.3.7     | Binary-Coded Decimal and Extended Instructions | 8-18 |

| 8.3.8     | Single Operand Instructions                    | 8-18 |

| 8.3.9     | Shift/Rotate Instructions                      | 8-19 |

| 8.3.10    | Bit Manipulation Instructions                  |      |

| 8.3.11    | Conditional Branch Instructions                | 8-20 |

| 8.3.12    | Control Instructions                           |      |

| 8.3.13    | Exception-Related Instructions and Operations  | 8-21 |

| 8.3.14    | Save and Restore Operations                    |      |

#### **APPENDIX AM68000 FAMILY SUMMARY**

#### **INDEX**

## **LIST OF ILLUSTRATIONS**

| Figure | Title                                               | Page  |

|--------|-----------------------------------------------------|-------|

| 1-1    | Loop Mode Instruction Sequence                      | 1-3   |

| 1-2    | CPU32 Block Diagram                                 |       |

| 2-1    | User Programming Model                              | 2-2   |

| 2-2    | Supervisor Programming Model Supplement             | 2-2   |

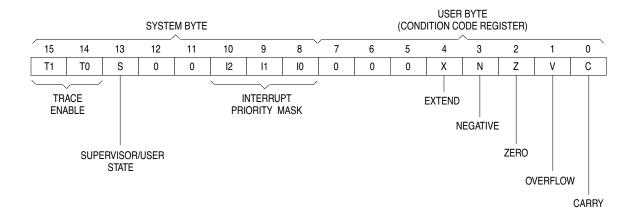

| 2-3    | Status Register                                     |       |

| 2-4    | Data Organization in Data Registers                 | 2-4   |

| 2-5    | Address Organization in Address Registers           | 2-5   |

| 2-6    | Memory Operand Addressing                           | 2-7   |

| 3-1    | Single-Effective-Address Instruction Operation Word | 3-1   |

| 3-2    | Effective Address Specification Formats             | 3-10  |

| 3-3    | Using SIZE in the Index Selection                   | 3-12  |

| 3-4    | Using Absolute Address with Indexes                 | 3-12  |

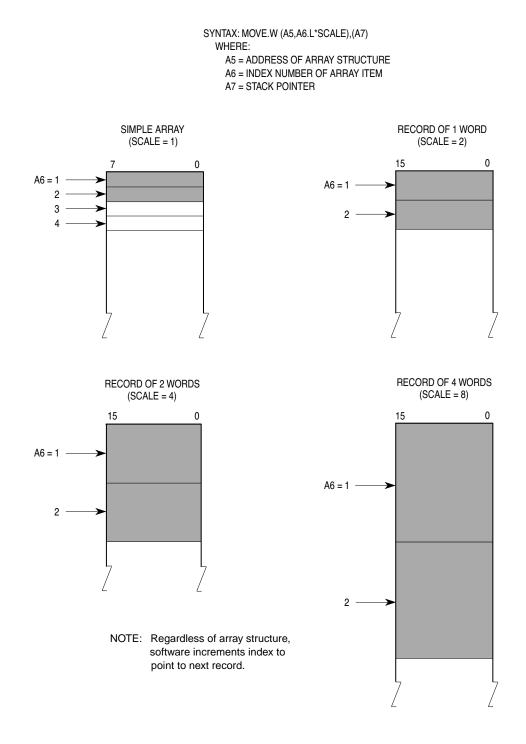

| 3-5    | Addressing Array Items                              | 3-13  |

| 3-6    | M68000 Family Address Extension Words               | 3-15  |

| 4-1    | Instruction Word General Format                     | 4-2   |

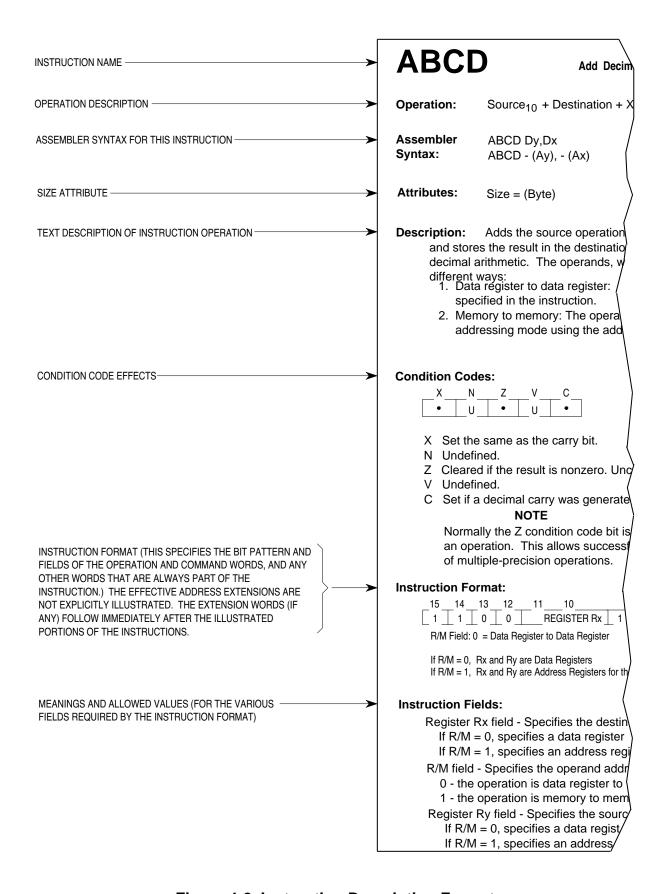

| 4-2    | Instruction Description Format                      | 4-14  |

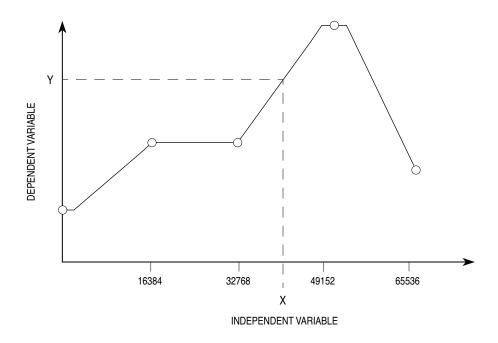

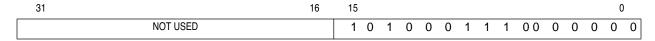

| 4-3    | Table Example 1                                     | 4-188 |

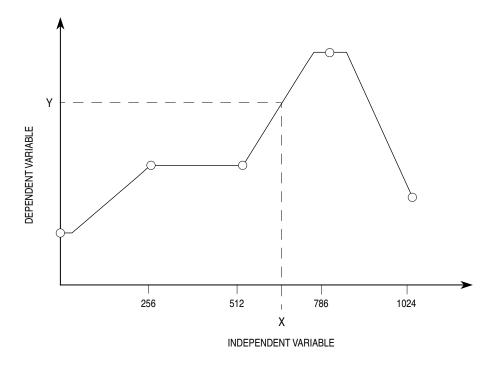

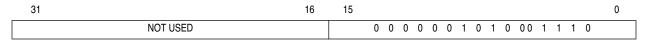

| 4-4    | Table Example 2                                     | 4-189 |

| 4-5    | Table Example 3                                     | 4-191 |

| 6-1    | Exception Stack Frame                               | 6-4   |

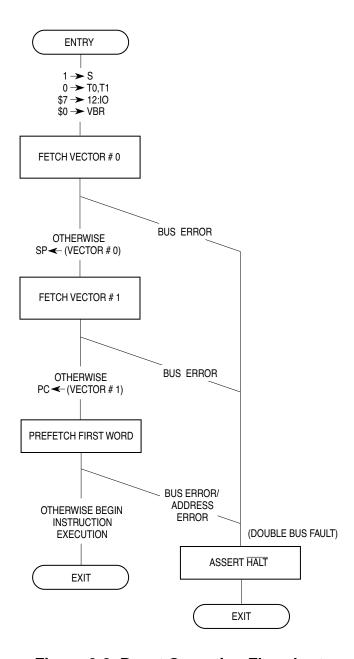

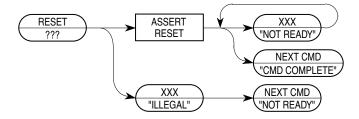

| 6-2    | Reset Operation Flowchart                           | 6-6   |

| 6-3    | Format \$0 — Four-Word Stack Frame                  | 6-22  |

| 6-4    | Format \$2 — Six-Word Stack Frame                   | 6-22  |

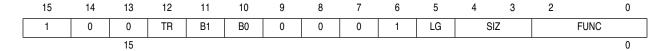

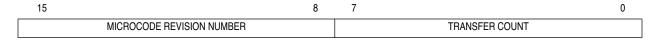

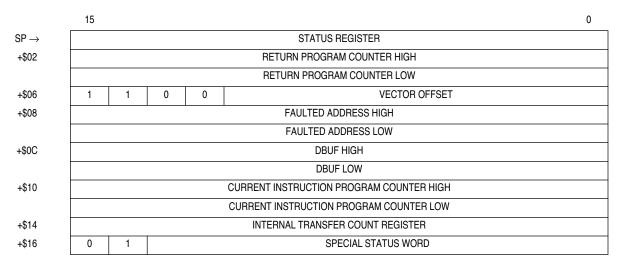

| 6-5    | Internal Transfer Count Register                    | 6-23  |

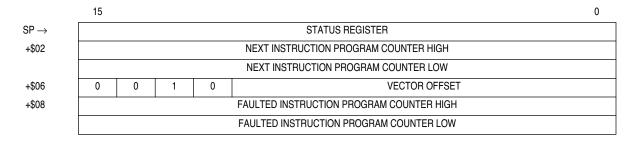

| 6-6    | Format \$C — BERR Stack for Prefetches and Operands | 6-24  |

| 6-7    | Format \$C — BERR Stack on MOVEM Operand            |       |

| 6-8    | Format \$C — Four- and Six-Word BERR Stack          |       |

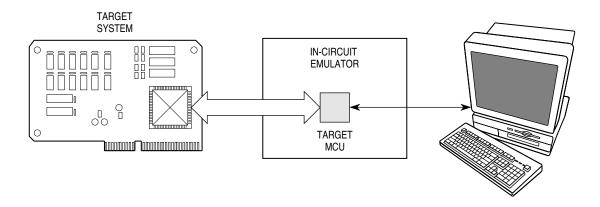

| 7-1    | In-Circuit Emulator Configuration                   | 7-2   |

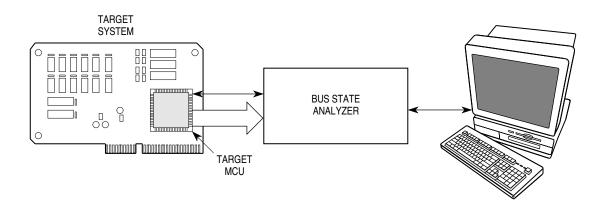

| 7-2    | Bus State Analyzer Configuration                    | 7-2   |

| 7-3    | BDM Block Diagram                                   | 7-3   |

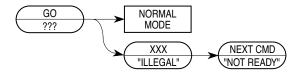

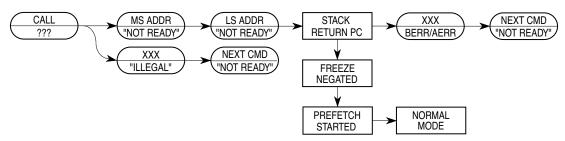

| 7-4    | BDM Command Execution Flowchart                     | 7-6   |

| 7-5    | Debug Serial I/O Block Diagram                      | 7-8   |

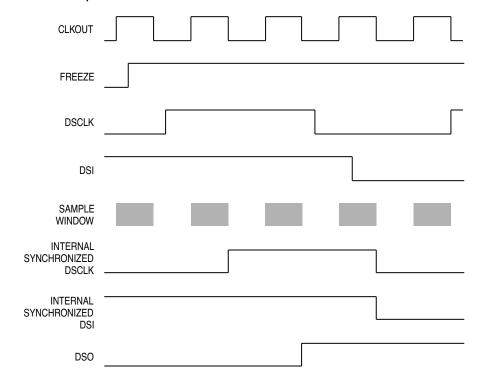

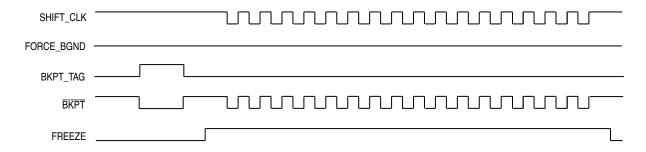

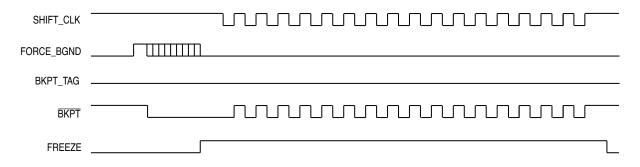

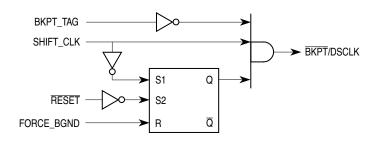

| 7-6    | Serial Interface Timing Diagram                     | 7-9   |

| 7-7    | BKPT Timing for Single Bus Cycle                    |       |

| 7-8    | BKPT Timing for Forcing BDM                         |       |

| 7-9    | BKPT/DSCLK Logic Diagram                            |       |

| 7-10   | Command-Sequence-Diagram Example                    |       |

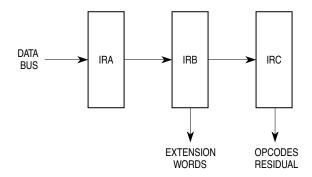

| 7-11   | Functional Model of Instruction Pipeline            |       |

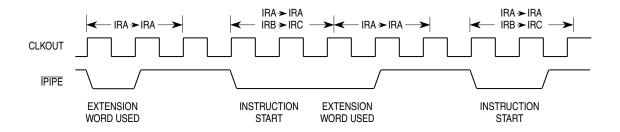

| 7-12   | Instruction Pipeline Timing Diagram                 |       |

| 8–1    | Block Diagram of Independent Resources              |       |

| 8-2    | Simultaneous Instruction Execution                  |       |

### LIST OF ILLUSTRATIONS (Continued) Title

| Figure | Title                            | Page |

|--------|----------------------------------|------|

| 8–3    | Attributed Instruction Times     | 8-4  |

| 8-4    | Example 1 — Instruction Stream   | 8-7  |

|        | Example 2 — Branch Taken         |      |

| 8-6    | Example 2 — Branch Not Taken     | 8-8  |

| 8-7    | Example 3 — Branch Negative Tail | 8-9  |

## **LIST OF TABLES**

| Tab  | ole Title                            | Page  |

|------|--------------------------------------|-------|

| 1-1  | Instruction Set Summary              | 1-5   |

| 3-1  | Effective Addressing Mode Categories | 3-11  |

|      | Condition Code Computations          |       |

| 4-2  | Data Movement Operations             | 4-6   |

|      | Integer Arithmetic Operations        |       |

| 4-4  | Logic Operations                     | 4-8   |

|      | Shift and Rotate Operations          |       |

| 4-6  | Bit Manipulation Operations          | 4-10  |

| 4-7  | Binary-Coded Decimal Operations      | 4-10  |

| 4-8  | Program Control Operations           | 4-10  |

| 4-9  | System Control Operations            | 4-11  |

| 4-10 | 0 Condition Tests                    | 4-12  |

| 4-1  | 1 Operation Code Map                 | 4-170 |

| 5-1  | Address Spaces                       | 5-3   |

| 6-1  | Exception Vector Assignments         | 6-2   |

| 6-2  | Exception Priority Groups            | 6-4   |

|      | Tracing Control                      |       |

| 7-1  | BDM Source Summary                   | 7-4   |

| 7-2  | Polling the BDM Entry Source         | 7-5   |

| 7-3  | CPU Generated Message Encoding       | 7-8   |

| 7-4  | BDM Command Summary                  | 7-14  |

| A-1  | M68000 instruction Set Extensions    | A-3   |

| A-2  | M68000 Addressing Modes              | A-4   |

## LIST OF TABLES (Continued) Title

Table Title Page

MOTOROLA CPU32 xiv REFERENCE MANUAL

#### **SECTION 1 OVERVIEW**

The CPU32, the first-generation instruction processing module of the M68300 Family, is based on the industry-standard MC68000 processor. It has many features of the MC68010 and MC68020, as well as unique features suited for high-performance controller applications. The CPU32 is source code and binary code compatible with the M68000 Family.

CPU32 power consumption during normal operation is low because it is a high-speed complementary metal-oxide semiconductor (HCMOS) device. Power consumption can be reduced to a minimum during periods of inactivity by executing the low-power stop (LPSTOP) instruction, which shuts down the CPU32 and other intermodule bus (IMB) submodules.

Ease of programming is an important consideration in using a microcontroller. The CPU32 instruction format reflects a predominately register-memory interaction philosophy. All data resources are available to all operations requiring those resources. There are eight multifunction data registers and seven general-purpose addressing registers. The data registers readily support 8-bit (byte), 16-bit (word), and 32-bit (long word) operand lengths for all operations. Address manipulation is supported by word and long-word operations. Although the program counter (PC) and stack pointers (SP) are special purpose registers, they are also available for most data addressing activities. Ease of program checking and diagnosis is enhanced by trace and trap capabilities at the instruction level.

As controller applications become more complex and control programs become larger, high-level language (HLL) will become the system designer's choice in programming languages. HLL aids rapid development of complex algorithms, with less error, and is readily portable. The CPU32 instruction set will efficiently support HLL.

#### 1.1 Features

Features of the CPU32 are as follows:

- Fully Upward Object Code Compatible with M68000 Family

- Virtual Memory Implementation

- Loop Mode of Instruction Execution

- Fast Multiply, Divide, and Shift Instructions

- Fast Bus Interface with Dynamic Bus Port Sizing

- Improved Exception Handling for Controller Applications

- Enhanced Addressing Modes

- Scaled Index

- Address Register Indirect with Base Displacement and

- Expanded PC Relative Modes

- 32-Bit Branch Displacements

- Instruction Set Enhancements

- High-Precision Multiply and Divide

- Trap On Condition Codes

- Upper and Lower Bounds Checking

- Enhanced Breakpoint Instruction

- Trace on Change of Flow

- Table Lookup and Interpolate Instruction

- Low-Power Stop Instruction

- Hardware Breakpoint Signal, Background Mode

- 16.77-MHz Operating Frequency (–40 to 125°C)

- Fully Static Implementation

#### 1.1.1 Virtual Memory

A system that supports virtual memory has a limited amount of high-speed physical memory that can be accessed directly by the processor and maintains an image of a much larger "virtual" memory on a secondary storage device. When the processor attempts to access a location in the virtual memory map that is not resident in physical memory, a page fault occurs. The access to that location is temporarily suspended while the necessary data is fetched from secondary storage and placed in physical memory. The suspended access is then restarted or continued. The CPU32 uses instruction restart, which requires that only a small portion of the internal machine state be saved. After correcting the fault, the machine state is restored, and the instruction is refetched and restarted. This process is completely transparent to the application program.

#### 1.1.2 Loop Mode Instruction Execution

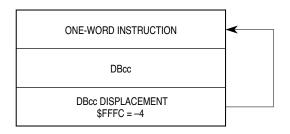

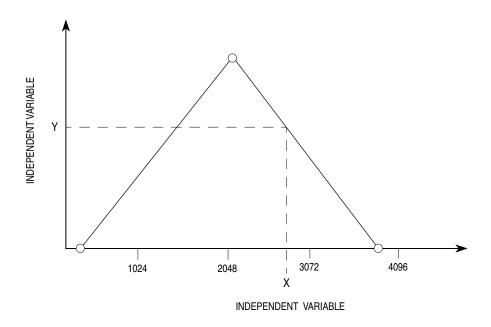

The CPU32 has several features that provide efficient execution of program loops. One of these features is the DBcc looping primitive. To increase the performance of the CPU32, a loop mode has been added to the processor. The loop mode is used by any single-word instruction that does not change the program flow. Loop mode is implemented in conjunction with the DBcc instruction. **Figure 1-1** shows the required form of an instruction loop for the processor to enter loop mode.

Loop mode is entered when DBcc is executed and loop displacement is –4. Once in loop mode, the processor performs only data cycles associated with the instruction and suppresses instruction fetches. Termination condition and count are checked after each execution of looped instruction data operations. The CPU automatically exits loop mode for interrupts or other exceptions.

Figure 1-1 Loop Mode Instruction Sequence

#### 1.1.3 Vector Base Register

The vector base register (VBR) contains the base address of the 1024-byte exception vector table. The table contains 256 exception vectors. Exception vectors are the memory addresses of routines that begin execution at the completion of exception processing. Each routine performs operations appropriate to the corresponding exception. Because exception vectors are memory addresses, each table entry is a single long word.

Each vector is assigned an 8-bit number. Vector numbers for some exceptions are obtained from an external device; others are supplied automatically by the processor. The processor multiplies the vector number by four to calculate vector offset, then adds the offset to the VBR base address. The sum is the memory address of the vector.

Because the VBR stores the vector table base address, the table can be located anywhere in memory. It can also be dynamically relocated for each task executed by an operating system. Details of exception processing are provided in **SECTION 6 EXCEPTION PROCESSING**.

#### 1.1.4 Exception Handling

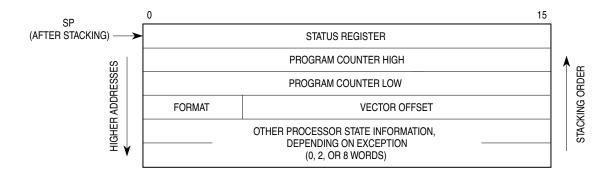

The processing of an exception occurs in four steps, with variations for different exception causes. During the first step, a temporary internal copy of the status register is made, and the status register is set for exception processing. During the second step, the exception vector is determined. During the third step, the current processor context is saved. During the fourth step, a new context is obtained, and the processor then proceeds with normal instruction execution.

Exception processing saves the most volatile portion of the current context by pushing it on the supervisor stack. This context is organized in a format called an exception stack frame. The stack frame always includes the status register and program counter at the time an exception occurs. To support generic handlers, the processor also places the vector offset in the exception stack frame and marks the frame with a format code. The return-from-exception (RTE) instruction uses the format code to determine what information is on the stack, so that context can be properly restored.

CPU32 **OVERVIEW** MOTOROLA 1-3

#### 1.1.5 Enhanced Addressing Modes

Addressing in the CPU32 is register oriented. Most instructions allow the results of the specified operation to be placed either in a register or in memory. There is no need for extra instructions to store register contents in memory.

There are seven basic addressing modes:

- 1. Register Direct

- 2. Register Indirect

- 3. Register Indirect with Index

- 4. Program Counter Indirect with Displacement

- 5. Program Counter Indirect with Index

- 6. Absolute

- 7. Immediate

The register indirect addressing modes include postincrement, predecrement, and offset capability. The PC relative mode also has index and offset capabilities. In addition to the addressing modes, many instructions implicitly specify the use of a status register, SP, and/or PC. Addressing is explained fully in **SECTION 3 DATA ORGANIZA-TION AND ADDRESSING CAPABILITIES**. A summary of M68000 Family addressing modes is found in **APPENDIX A M68000 FAMILY SUMMARY**.

#### 1.1.6 Instruction Set

The instruction set of the CPU32 is very similar to that of the MC68020 (see Table 1-1). Two new instructions have been added to facilitate controller applications — low-power stop (LPSTOP) and table lookup and interpolate (TBL). The following M68020 instructions **are not implemented** on the CPU32:

```

BFxxx — Bit Field Instructions (BFCHG, BFCLR, BFEXTS, BFEXTU, BFFFO BFINS, BFSET, BFTST)

CALLM, RTM — Call Module, Return Module

CAS, CAS2 — Compare and Set (Read-Modify-Write Instructions)

cpxxx Coprocessor Instructions (cpBcc, cpDBcc, cpGEN, cp RESTORE, cpSAVE, cpScc, cpTRAPcc)

PACK, UNPK Pack, Unpack BCD Instructions

```

The CPU32 traps on unimplemented instructions and illegal effective addressing modes, allowing the user to emulate instructions or to define special-purpose functions. However, Motorola reserves the right to use all currently uniplemented instructions operation codes for future M68000 core enhancements.

See **SECTION 4 INSTRUCTION SET** for comprehensive information.

#### 1.1.6.1 Table Lookup and Interpolation Instructions

To speed up real-time applications, a range of discrete data points is often precalculated from a continuous control function, then stored in memory. A full range of data can require an inordinate amount of memory. The table instructions make it possible

to store a sample of the full range and recover intermediate values quickly via linear interpolation. A round-to-nearest algorithm can be applied to the results.

**Table 1-1 Instruction Set Summary**

| Mnemonic    | Description                                     |

|-------------|-------------------------------------------------|

| ABCD        | Add Decimal with Extend                         |

| ADD         | Add                                             |

| ADDA        | Add Address                                     |

| ADDI        | Add Immediate                                   |

| ADDQ        | Add Quick                                       |

| ADDX        | Add with Extend                                 |

| AND         | Logical AND                                     |

| ANDI        | Logical AND Immediate                           |

| ASL, ASR    | Arithmetic Shift Left and Right                 |

| Bcc         | Branch Conditionally                            |

| BCHG        | Test Bit and Change                             |

| BCLR        | Test Bit and Clear                              |

| BGND        | Background                                      |

| BKPT        | Breakpoint                                      |

| BRA         | Branch                                          |

| BSET        | Test Bit and Set                                |

| BSR         | Branch to Subroutine                            |

| BTST        | Test Bit                                        |

| CHK, CHK2   | Check Register Against Upper and Lower Bounds   |

| CLR         | Clear                                           |

| CMP         | Compare                                         |

| CMPA        | Compare Address                                 |

| CMPI        | Compare Immediate                               |

| CMPM        | Compare Memory to Memory                        |

| CMP2        | Compare Register Against Upper and Lower Bounds |

| DBcc        | Test Condition, Decrement and Branch            |

| DIVS, DIVSL | Signed Divide                                   |

| DIVU, DIVUL | Unsigned Divide                                 |

| EOR         | Logical Exclusive OR                            |

| EORI        | Logical Exclusive OR Immediate                  |

| EXG         | Exchange Registers                              |

| EXT, EXTB   | Sign Extend                                     |

| LEA         | Load Effective Address                          |

| LINK        | Link and Allocate                               |

| LPSTOP      | Low Power Stop                                  |

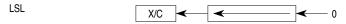

| LSL, LSR    | Logical Shift Left and Right                    |

| ILLEGAL     | Take Illegal Instruction Trap                   |

| JMP         | Jump                                            |

| JSR         |                                                 |

| Mnemonic     | Description                       |

|--------------|-----------------------------------|

|              | Description                       |

| MOVE         | Move                              |

| MOVE CCR     | Move Condition Code Register      |

| MOVE SR      | Move Status Register              |

| MOVE USP     | Move User Stack Pointer           |

| MOVEA        | Move Address                      |

| MOVEC        | Move Control Register             |

| MOVEM        | Move Multiple Registers           |

| MOVEP        | Move Peripheral                   |

| MOVEQ        | Move Quick                        |

| MOVES        | Move Alternate Address Space      |

| MULS, MULS.L | Signed Multiply                   |

| MULU, MULU.L | Unsigned Multiply                 |

| NBCD         | Negate Decimal with Extend        |

| NEG          | Negate                            |

| NEGX         | Negate with Extend                |

| NOP          | No Operation                      |

| OR           | Logical Inclusive OR              |

| ORI          | Logical Inclusive OR Immediate    |

| PEA          | Push Effective Address            |

|              |                                   |

| RESET        | Reset External Devices            |

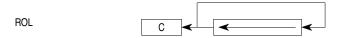

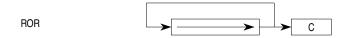

| ROL, ROR     | Rotate Left and Right             |

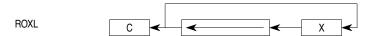

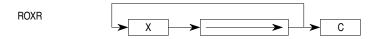

| ROXL, ROXR   | Rotate with Extend Left and Right |

| RTD          | Return and Deallocate             |

| RTE          | Return from Exception             |

| RTR          | Return and Restore Codes          |

| RTS          | Return from Subroutine            |

| SBCD         | Subtract Decimal with Extend      |

| Scc          | Set Conditionally                 |

| STOP         | Stop                              |

| SUB          | Subtract                          |

| SUBA         | Subtract Address                  |

| SUBI         | Subtract Immediate                |

| SUBQ         | Subtract Quick                    |

| SUBX         | Subtract with Extend              |

| SWAP         | Swap Register Words               |

| TBLS, TBLSN  | Table Lookup and Interpolate      |

|              | (Signed)                          |

| TBLU, TBLUN  | Table Lookup and Interpolate      |

|              | (Unsigned)                        |

| TAS          | Test Operand and Set              |

| TRAP         | Trap                              |

|              | Trap Conditionally                |

| TRAPCC       |                                   |

|              | Trap on Overflow                  |

| TST          | Test Operand                      |

| UNLK         | Unlink                            |

#### 1.1.6.2 Low-Power Stop Instruction

The CPU32 is a fully static design. Power consumption can be reduced to a minimum during periods of inactivity by stopping the system clock. The CPU32 instruction set includes a low-power stop command (LPSTOP) that efficiently implements this capability. The processor will remain in stop mode until a user-specified interrupt, or reset, occurs.

#### 1.1.7 Processing States

There are four processing states — normal, exception, background and halted.

Normal processing is associated with instruction execution. The bus is used to fetch instructions and operands, and to store results.

Exception processing is associated with interrupts, trap instructions, tracing, and other exception conditions.

Background processing allows interactive debugging of the system.

Halted processing is an indication of catastrophic hardware failure.

See **SECTION 5 PROCESSING STATES** for complete information.

#### 1.1.8 Privilege States

The processor can operate at either of two privilege levels. Supervisor level is more privileged than user level — all instructions are available at supervisor level, but access is restricted at user level.

Effective use of privilege level can protect system resources from uncontrolled access. The state of the S bit in the status register determines access level and whether the stack pointer (USP) or the supervisor stack pointer (SSP) is used for stack operations.

See **SECTION 5 PROCESSING STATES** for a complete explanation of privilege levels.

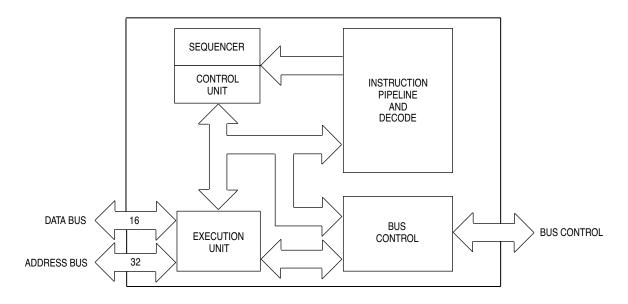

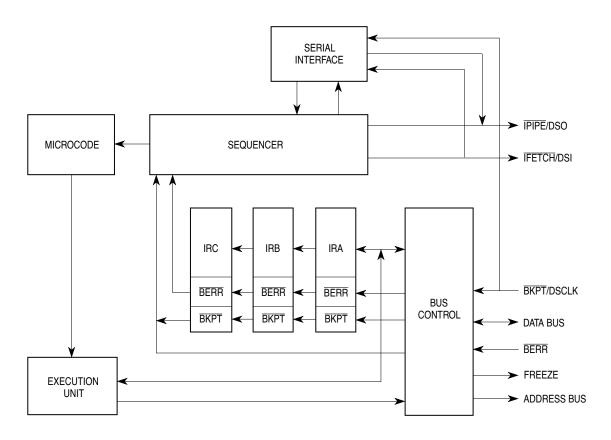

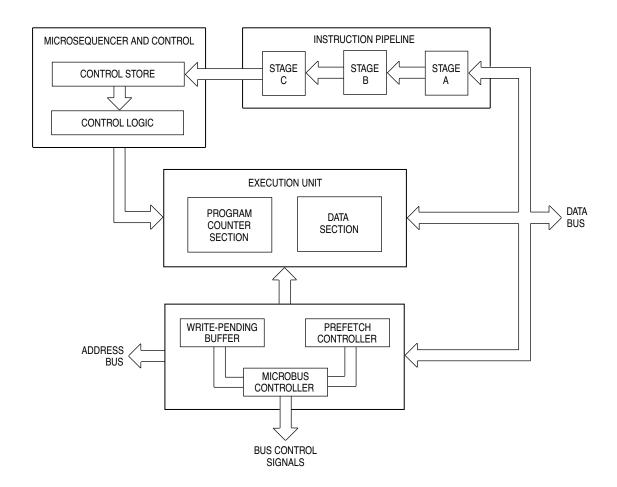

#### 1.2 Block Diagram

A block diagram of the CPU32 is shown in **Figure 1-2**. The functional elements operate concurrently. Essential synchronization of instruction execution and buss operation is maintained by the sequencer/control unit. The bus controller prefetches instructions and operands. A three-stage pipeline is used to hold and decode instructions prior to execution. The execution unit maintains the program counter under sequencer control. The bus control contains a write-pending buffer that allows the sequencer to continue execution of instructions after a request for a write cycle is queued. See **SECTION 8 INSTRUCTION EXECUTION TIMING** for a detailed explanation of instruction execution.

Figure 1-2 CPU32 Block Diagram

#### **SECTION 2ARCHITECTURE SUMMARY**

The CPU32 is upward source and object code compatible with the MC68000 and MC68010. It is downward source and object code compatible with the MC68020. Within the M68000 Family, architectural differences are limited to the supervisory operating state. User state programs can be executed unchanged on upward compatible devices.

The major CPU32 features are as follows:

- 32-Bit Internal Data Path and Arithmetic Hardware

- 32-Bit Address Bus Supported by 32-Bit Calculations

- Rich Instruction Set

- Eight 32-Bit General-Purpose Data Registers

- Seven 32-Bit General-Purpose Address Registers

- Separate User and Supervisor Stack Pointers

- Separate User and Supervisor State Address Spaces

- Separate Program and Data Address Spaces

- Many Data Types

- Flexible Addressing Modes

- Full Interrupt Processing

- Expansion Capability

#### 2.1 Programming Model

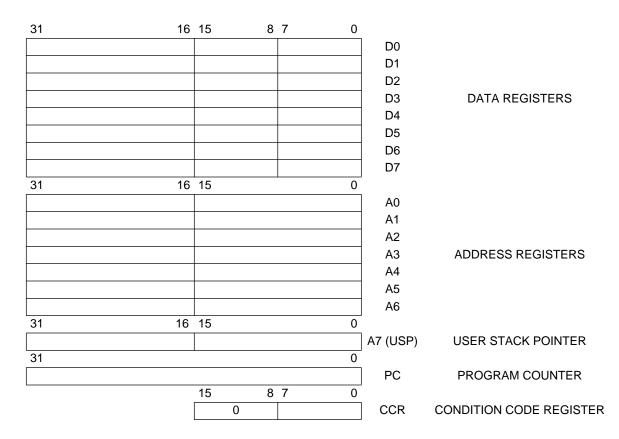

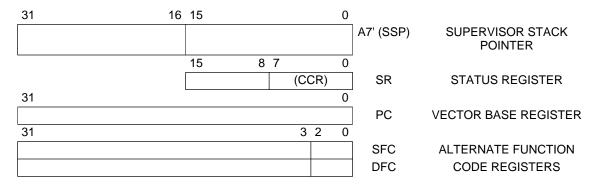

The CPU32 programming model consists of two groups of registers that correspond to the user and supervisor privilege levels. User programs can only use the registers of the user model. The supervisor programming model, which supplements the user programming model, is used by CPU32 system programmers who wish to protect sensitive operating system functions. The supervisor model is identical to that of MC68010 and later processors.

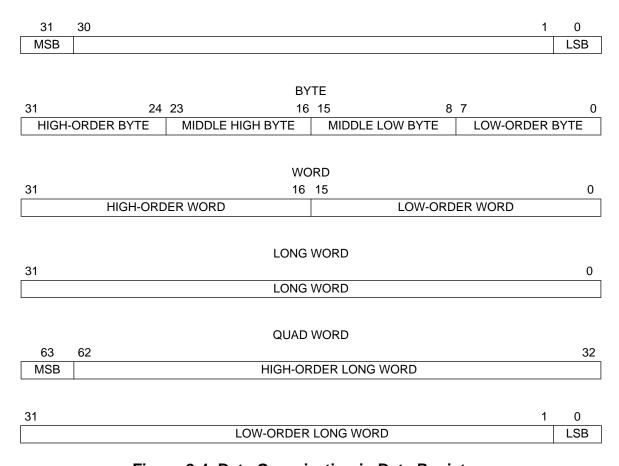

The CPU32 has eight 32-bit data registers, seven 32-bit address registers, a 32-bit program counter, separate 32-bit supervisor and user stack pointers, a 16-bit status register, two alternate function code registers, and a 32-bit vector base register (see **Figure 2-1** and **Figure 2-2**).

Figure 2-1 User Programming Model

Figure 2-2 Supervisor Programming Model Supplement

#### 2.2 Registers

Registers D7 to D0 are used as data registers for bit, byte (8-bit), word (16-bit), longword (32-bit), and quad-word (64-bit) operations. Registers A6 to A0 and the user and supervisor stack pointers are address registers that may be used as software stack pointers or base address registers. Register A7 (shown as A7 and A7' in **Figure 2-1**) is a register designation that applies to the user stack pointer in the user privilege level and to the supervisor stack pointer in the supervisor privilege level. In addition, address registers may be used for word and long-word operations. All of the 16 general-purpose registers (D7 to D0, A7 to A0) may be used as index registers.

The program counter (PC) contains the address of the next instruction to be executed by the CPU32. During instruction execution and exception processing, the processor automatically increments the contents of the PC or places a new value in the PC, as appropriate.

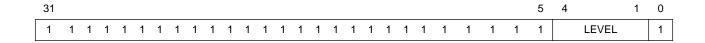

The status register (SR) (see **Figure 2-3**) contains condition codes, an interrupt priority mask (three bits), and three control bits. Condition codes reflect the results of a previous operation. The codes are contained in the low byte, or condition code register of the SR. The interrupt priority mask determines the level of priority an interrupt must have in order to be acknowledged. The control bits determine trace mode and privilege level. At user privilege level, only the condition code register is available. At supervisor privilege level, software can access the full status register.

Figure 2-3 Status Register

The vector base register (VBR) contains the base address of the exception vector table in memory. The displacement of an exception vector is added to the value in this register to access the vector table.

Alternate function code registers SFC and DFC contain 3-bit function codes. The CPU32 generates a function code each time it accesses an address. Specific codes are assigned to each type of access. The codes can be used to select eight dedicated 4G-byte address spaces. The MOVE instructions can use registers SFC and DFC to specify the function code of a memory address.

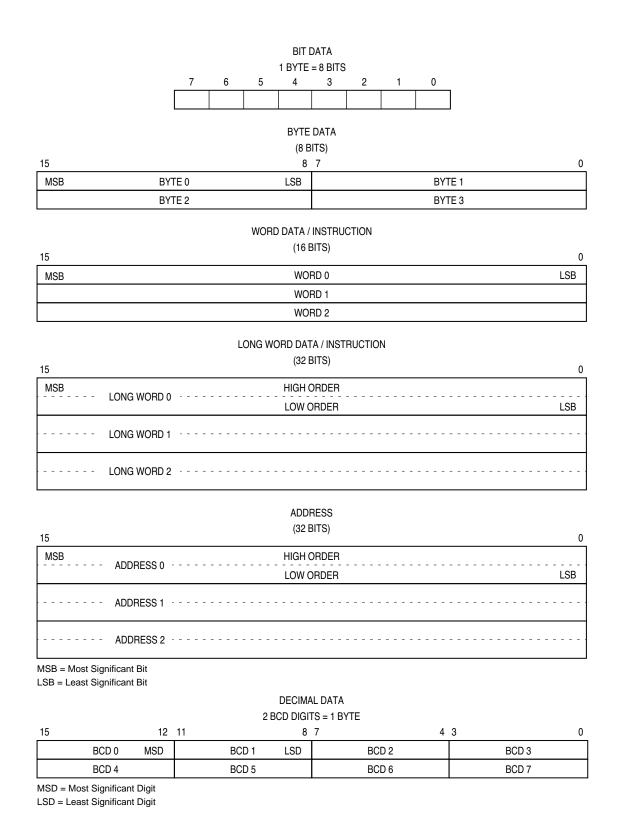

#### 2.3 Data Types

Six basic data types are supported:

- 1. Bits

- Binary-Coded Decimal (BCD) Digits

- 3. Byte Integers (8 bits)

- 4. Word Integers (16 bits)

- 5. Long-Word Integers (32 bits)

- Quad-Word Integers (64 bits)

#### 2.3.1 Organization in Registers

The eight data registers can store data operands of 1, 8, 16, 32, and 64 bits and addresses of 16 or 32 bits. The seven address registers and the two stack pointers are used for address operands of 16 or 32 bits. The PC is 32 bits wide.

#### 2.3.1.1 Data Registers

Each data register is 32 bits wide. Byte operands occupy the low-order 8 bits, word operands, the low-order 16 bits, and long-word operands, the entire 32 bits. When a data register is used as either a source or destination operand, only the appropriate low-order byte or word (in byte or word operations, respectively) is used or changed — the remaining high-order portion is neither used nor changed. The least significant bit (LSB) of a long-word integer is addressed as bit zero, and the most significant bit (MSB) is addressed as bit 31. **Figure 2-4** shows the organization of various types of data in the data registers.

Figure 2-4 Data Organization in Data Registers

Quad-word data consists of two long words: for example, the product of 32-bit multiply or the quotient of 32-bit divide operations (signed and unsigned). Quad words may be organized in any two data registers without restrictions on order or pairing. There are no explicit instructions for the management of this data type; however, the MOVEM instruction can be used to move a quad word into or out of the registers.

BCD data represents decimal numbers in binary form. CPU32 BCD instructions use a format in which a byte contains two digits — the four LSB contain the low digit, and the four MSB contain the high digit. The ABCD, SBCD, and NBCD instructions operate on two BCD digits packed into a single byte.

#### 2.3.1.2 Address Registers

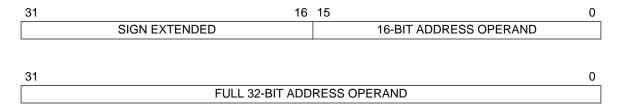

Each address register and stack pointer holds a 32-bit address. Address registers cannot be used for byte-sized operands. When an address register is used as a source operand, either the low-order word or the entire long-word operand is used, depending upon the operation size. When an address register is used as a destination operand, the entire register is affected, regardless of operation size. If the source operand is a word, it is first sign extended to 32 bits, and then used in the operation. Address registers can be used to support address computation. The instruction set includes instructions that add to, subtract from, compare, and move the contents of address registers. **Figure 2-5** shows the organization of addresses in address registers.

Figure 2-5 Address Organization in Address Registers

#### 2.3.1.3 Control Registers

The control registers contain control information for supervisor functions. The registers vary in size. With the exception of the user portion of the SR (CCR), they are accessed only by instructions at the supervisor privilege level.

The SR shown in **Figure 2-3** is 16 bits wide. Only 11 bits of the SR are defined, and all undefined values are reserved by Motorola for future definition. The undefined bits are read as zeros and should be written as zeros for future compatibility. The lower byte of the SR is the CCR. Operations to the CCR can be performed at the supervisor or user privilege level. All operations to the SR and CCR are word-size operations. For all CCR operations, the upper byte is read as all zeros and is ignored when written, regardless of privilege level.

The alternate function code registers (SFC and DFC) are 32-bit registers with only bits [2:0] implemented. These bits contain address space values (FC2 to FC0) for the read or write operand of the MOVES instruction. The MOVEC instruction is used to transfer values to and from the alternate function code registers. These are long-word transfers — the upper 29 bits are read as zeros and are ignored when written.

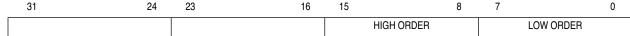

#### 2.3.2 Organization in Memory

Memory is organized on a byte-addressable basis. An address corresponds to a high-order byte. For example, the address (N) of a long-word data item is the address of the most significant byte of the high-order word. The address of the most significant byte of the low-order word is (N+2), and the address of the least significant byte of the long word is (N+3). The CPU32 requires data words and long words, as well as instruction words to be aligned on word boundaries. Data misalignment is not supported. **Figure 2-6** shows how operands and instructions are organized in memory. Note that (N+X) is below (N) — that is, address value increases as one moves down the page.

Figure 2-6 Memory Operand Addressing

#### SECTION 3 DATA ORGANIZATION AND ADDRESSING CAPABILITIES

The addressing mode of an instruction can specify the value of an operand (an immediate operand), a register that contains the operand (register direct addressing mode), or how the effective address of an operand in memory is derived. An assembler syntax has been defined for each addressing mode.

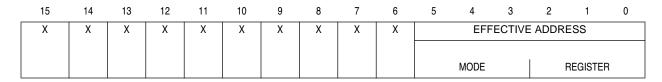

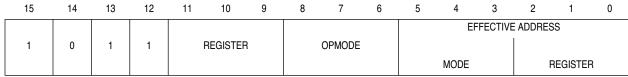

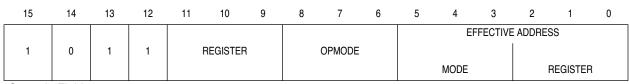

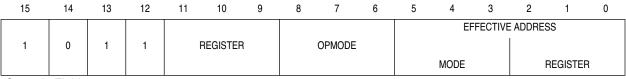

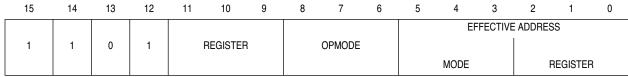

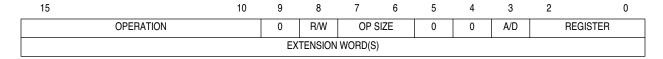

**Figure 3-1** shows the general format of the single-effective-address instruction operation word. The effective address field specifies the addressing mode for an operand that can use one of the numerous defined modes. The designation is composed of two 3-bit fields, the mode field and the register field. The value in the mode field selects a mode or a set of modes. The register field specifies a register for the mode or a submode for modes that do not use registers.

Figure 3-1 Single-Effective-Address Instruction Operation Word

Many instructions imply the addressing mode for only one of the operands. The formats of these instructions include appropriate fields for operands that use only a single addressing mode.

Additional information may be needed to specify an operand address. This information is contained in an additional word or words called the effective address extension, and is considered part of an instruction. Address extension formats are discussed in **3.4.4 Effective Address Encoding Summary**.

When an addressing mode uses a register, the register is specified by the register field of the operation word. Other fields within the instruction specify whether the selected register is an address or data register and how the register is to be used.

#### 3.1 Program and Data References

An M68000 Family processor makes two classes of memory references, each of which has a complete, separate logical address space.

References to opcodes and extension words are program space references.

Operand reads and writes are primarily data space references. Operand reads are from data space in all but two cases — immediate operands embedded in the instruction stream and operands addressed relative to the current program counter are program space references. All operand writes are to data space.

#### 3.2 Notation Conventions

EA — Effective address

An — Address register n

Example: A3 is address register 3

Dn — Data register n

Example: D5 is data register 5 Rn — Any register, data or address

Xn.SIZE\*SCALE —

Index register n (data or address),

Index size (W for word, L for long word),

Scale factor (1, 2, 4, or 8 for byte, word, long-word or quad-word scaling)

PC — Program counter

SR — Status register

SP — Stack pointer

CCR — Condition code register

USP — User stack pointer

SSP — Supervisor stack pointer

dn — Displacement value, n bits wide

bd — Base displacement

L — Long-word size

W — Word size

B — Byte size

(An) — Identifies an indirect address in a register

#### 3.3 Implicit Reference

Some instructions make implicit reference to the program counter, the system stack pointer, the user stack pointer, the supervisor stack pointer, or the status register. The following table shows the instructions and the registers involved:

| Instruction      | Implicit Registers |

|------------------|--------------------|

| ANDI to CCR      | SR                 |

| ANDI to SR       | SR                 |

| BRA              | PC                 |

| BSR              | PC, SP             |

| CHK (exception)  | PC, SP             |

| CHK2 (exception) | SSP, SR            |

| DBcc             | PC                 |

| DIVS (exception) | SSP, SR            |

| DIVU (exception) | SSP, SR            |

| EORI to CCR      | SR                 |

| EORI to SR       | SR                 |

| JMP              | PC                 |

| JSR              | PC, SP             |

| LINK             | SP                 |

| LPSTOP           | SR                 |

| MOVE CCR         | SR                 |

| MOVE SR          | SR                 |

| MOVE USP         | USP                |

| Instruction       | Implicit Registers |

|-------------------|--------------------|

| ORI to CCR        | SR                 |

| ORI to SR         | SR                 |

| PEA               | SP                 |

| RTD               | PC, SP             |

| RTE               | PS, SP, SR         |

| RTR               | PC, SP, SR         |

| RTS               | PC, SP             |

| STOP              | SR                 |

| TRAP (exception)  | SSP, SR            |

| TRAPV (exception) | SSP, SR            |

| UNLK              | SP                 |

#### 3.4 Effective Address

Most instructions specify the location of an operand by a field in the operation word called an effective address field or an effective address ( $\langle EA \rangle$ ). An EA is composed of two 3-bit subfields: mode specification field and register specification field. Each of the address modes is selected by a particular value in the mode specification subfield of the EA. The EA field may require further information to fully specify the operand. This information, called the EA extension, is in a following word or words and is considered part of the instruction (see **3.1 Program and Data References**).

#### 3.4.1 Register Direct Mode

These EA modes specify that the operand is in one of the 16 multifunction registers.

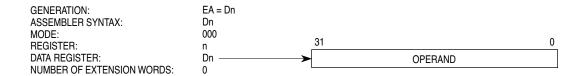

#### 3.4.1.1 Data Register Direct

In the data register direct mode, the operand is in the data register specified by the EA register field.

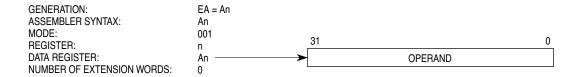

#### 3.4.1.2 Address Register Direct

In the address register direct mode, the operand is in the address register specified by the EA register field.

#### 3.4.2 Memory Addressing Modes

These EA modes specify the address of the memory operand.

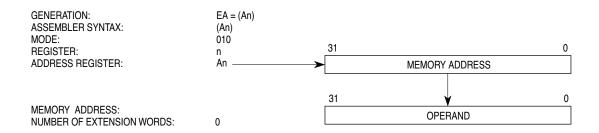

#### 3.4.2.1 Address Register Indirect

In the address register indirect mode, the operand is in memory, and the address of the operand is in the address register specified by the register field.

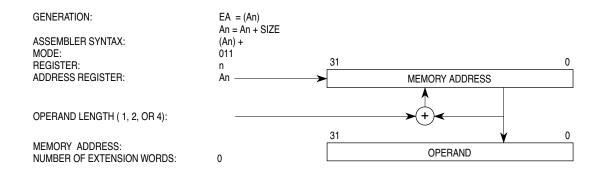

#### 3.4.2.2 Address Register Indirect With Postincrement

In the address register indirect with postincrement mode, the operand is in memory, and the address of the operand is in the address register specified by the register field. After the operand address is used, it is incremented by one, two, or four, depending on the size of the operand: byte, word, or long word. If the address register is the stack pointer and the operand size is byte, the address is incremented by two rather than one to keep the stack pointer aligned to a word boundary.

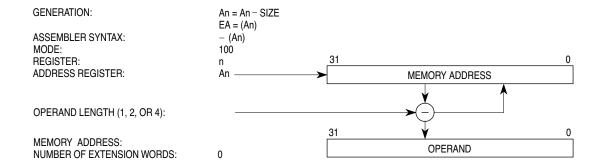

#### 3.4.2.3 Address Register Indirect With Predecrement

In the address register indirect with predecrement mode, the operand is in memory, and the address of the operand is in the address register specified by the register field. Before the operand address is used, it is decremented by one, two, or four, depending on the operand size: byte, word, or long word. If the address register is the stack pointer and the operand size is byte, the address is decremented by two rather than one to keep the stack pointer aligned to a word boundary.

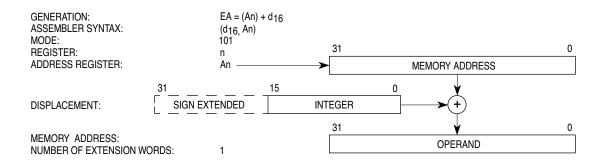

#### 3.4.2.4 Address Register Indirect With Displacement

In the address register indirect with displacement mode, the operand is in memory. The address of the operand is the sum of the address in the address register plus the sign-extended 16-bit displacement integer in the extension word. Displacements are always sign extended to 32 bits before being used in EA calculations.

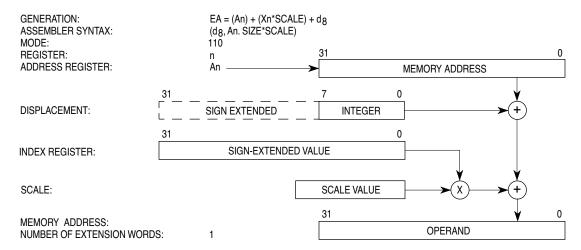

#### 3.4.2.5 Address Register Indirect With Index (8-Bit Displacement)

This mode requires one extension word that contains the index register indicator and an 8-bit displacement. The index register indicator includes size and scale information. In this mode, the operand is in memory. The address of the operand is the sum of the contents of the address register, the sign-extended displacement value in the low-order eight bits of the extension word, and the sign-extended contents of the index register (possibly scaled). The user must specify displacement, address register, and index register.

This address mode can have either of two different formats of extension. The brief format (8-bit displacement) requires one word of extension and provides fast indexed addressing. The full format (16 and 32-bit displacement) provides optional displacement size. Both forms use an index operand.

For brief format addressing, the address of the operand is the sum of the address in the address register, the sign-extended displacement integer in the low-order eight bits of the extension word, and the index operand. The reference is classed as a data reference, except for the JMP and JSR instructions. The index operand is specified "Ri.sz\*scl".

CPU32

"Ri" specifies a general data or address register used as an index register. The index operand is derived from the index register. The index register is a data register if bit [15] = 0 in the first extension word and an address register if bit [15] = 1. The index register number is given by extension word bits [14:12].

Index size is referred to as "sz". It may be either "W" or "L". Index size is given by bit [11] of the extension word. If bit [11] = 0, the index value is the sign-extended low-order word integer of the index register (W). If bit [11] = 1, the index value is the long integer in the index register (L).

The term "scl" refers to index scale selection and may be 1, 2, 4, or 8. The index value is scaled according to bits [10:9]. Codes 00, 01, 10, or 11 select index scaling of 1, 2, 4, or 8, respectively.

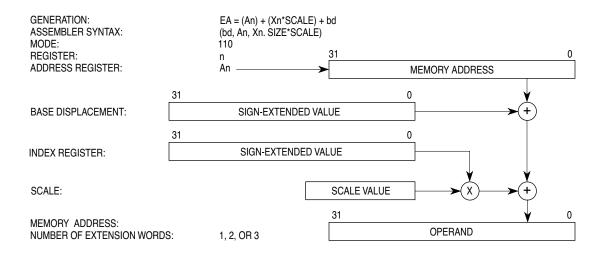

#### 3.4.2.6 Address Register Indirect With Index (Base Displacement)

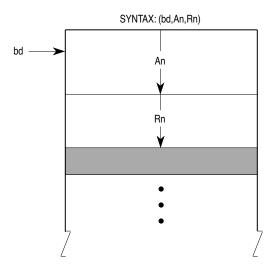

The full format indexed addressing mode requires an index register indicator and an optional 16- or 32-bit sign-extended base displacement. The index register indicator includes size and scale information. In this mode, the operand is in memory. The address of the operand is the sum of the contents of the address register, the scaled contents of the sign-extended index register, and the base displacement.

## 3.4.3 Special Addressing Modes

These special addressing modes do not use the register field to specify a register number but rather to specify a submode.

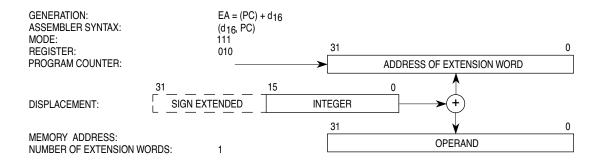

## 3.4.3.1 Program Counter Indirect With Displacement

In this mode, the operand is in memory. The address of the operand is the sum of the address in the program counter and the sign-extended 16-bit displacement integer in the extension word. The value in the program counter is the address of the extension word. The reference is a program space reference and is only allowed for read accesses.

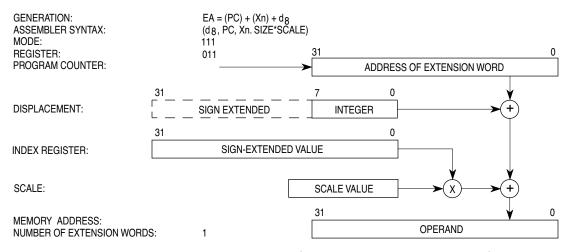

## 3.4.3.2 Program Counter Indirect with Index (8-Bit Displacement)

This mode is similar to the address register indirect with index (8-bit displacement) mode described in 3.4.2.5 Address Register Indirect With Index (8-Bit Displacement), but the program counter is used as the base register.

The operand is in memory. The address of the operand is the sum of the address in the program counter, the sign-extended displacement integer in the lower eight bits of the extension word, and the sized, scaled, and sign-extended index operand. The value in the program counter is the address of the extension word. This reference is a program space reference and is only allowed for reads. The user must include the displacement, the program counter, and the index register when specifying this addressing mode.

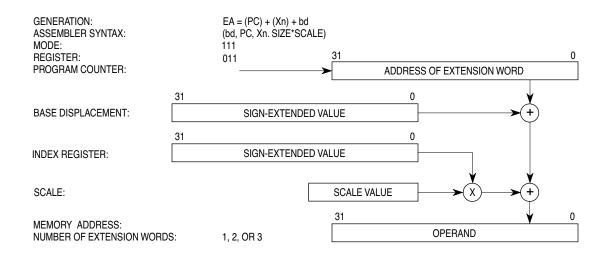

## 3.4.3.3 Program Counter Indirect with Index (Base Displacement)

This mode is similar to the address register indirect with index (base displacement) mode described in **3.4.2.6 Address Register Indirect With Index (Base Displacement)**, but the program counter is used as the base register. It requires an index register indicator and an optional 16- or 32-bit sign-extended base displacement.

The operand is in memory. The address of the operand is the sum of the contents of the program counter, the scaled contents of the sign-extended index register, and the base displacement. The value of the program counter is the address of the first extension word. The reference is a program space reference and is only allowed for read accesses.

In this mode, the program counter, the index register, and the displacement are all optional. However, the user must supply the assembler notation "ZPC" (zero value is taken for the program counter) to indicate that the program counter is not used. This scheme allows the user to access the program space without using the program counter in calculating the EA. The user can access the program space with a data register indirect access by placing ZPC in the instruction and specifying a data register (Dn) as the index register.

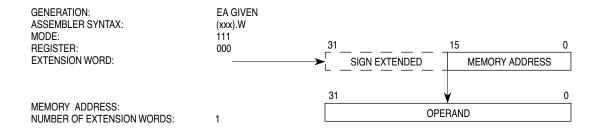

#### 3.4.3.4 Absolute Short Address

In this addressing mode, the operand is in memory, and the address of the operand is in the extension word. The 16-bit address is sign extended to 32 bits before it is used.

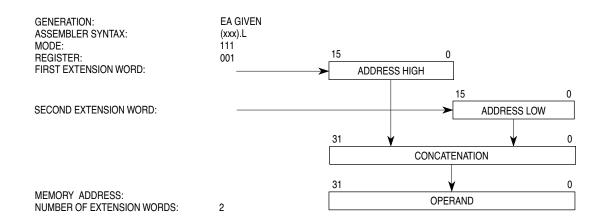

#### 3.4.3.5 Absolute Long Address

In this mode, the operand is in memory, and the address of the operand occupies the two extension words following the instruction word in memory. The first extension word contains the high-order part of the address; the low-order part of the address is the second extension word.

#### 3.4.3.6 Immediate Data

In this addressing mode, the operand is in one or two extension words:

## Byte Operation

The operand is in the low-order byte of the extension word.

#### **Word Operation**

The operand is in the extension word.

#### Long-Word Operation

The high-order 16 bits of the operand are in the first extension word; the low-order 16 bits are in the second extension word.

GENERATION: OPERAND GIVEN ASSEMBLER SYNTAX: #XXX

MODE: 1111

REGISTER: 100

NUMBER OF EXTENSION WORDS: 1 OR 2

#### 3.4.4 Effective Address Encoding Summary

Most addressing modes use one of the three formats shown in **Figure 3-2**. The single EA instruction is in the format of the instruction word. The mode field of this word selects the addressing mode. The register field contains the general register number or a value that selects the addressing mode when the mode field contains "111".

Some indexed or indirect modes use the instruction word followed by the brief format extension word. Other indexed or indirect modes consist of the instruction word and the full format of extension words. The longest instruction for the CPU32 contains six extension words. It is a MOVE instruction with full format extension words for both source and destination EA and a 32-bit base displacement for both addresses.

CPU32 DATA ORGANIZATION AND ADDRESSING CAPABILITIES

|     |                                      |        |    |     | ;         | SINGLE E | A INSTRU | JCTION F     | ORMAT |    |      |        |       |        |   |

|-----|--------------------------------------|--------|----|-----|-----------|----------|----------|--------------|-------|----|------|--------|-------|--------|---|

| 15  | 14                                   | 13     | 12 | 11  | 10        | 9        | 8        | 7            | 6     | 5  | 4    | 3      | 2     | 1      | 0 |

|     |                                      |        |    |     |           |          |          |              |       |    | EFF  | ECTIVE | ADDRE | ESS    |   |

| X   | Х                                    | Х      | Х  | Х   | Χ         | Х        | Х        | Х            | Х     |    |      |        |       |        |   |

|     |                                      |        |    |     |           |          |          |              |       |    | MODE |        | R     | EGISTE | R |

|     |                                      |        |    |     |           |          |          | •            | •     |    |      |        | •     |        |   |

|     |                                      |        |    |     | 1         | BRIEF FO | RMAT EX  | TENSION      | WORD  |    |      |        |       |        |   |

| 15  | 14                                   |        | 12 | 11  | 10        | 9        | 8        | 7            |       |    |      |        |       |        | 0 |

| D/A | R                                    | EGISTE | R  | W/L | SC        | ALE      | 0        | DISPLACEMENT |       |    |      |        |       |        |   |

|     |                                      |        |    |     |           |          |          |              |       |    |      |        |       |        |   |

|     | FULL FORMAT EXTENSION WORD(S)        |        |    |     |           |          |          |              |       |    |      |        |       |        |   |

| 15  | 14                                   |        | 12 | 11  | 10        | 9        | 8        | 7            | 6     | 5  | 4    | 3      | 2     |        | 0 |

| D/A | R                                    | EGISTE | R  | W/L | W/L SCALE |          | 1        | BS           | IS    | BD | SIZE | 0      |       | I/IS   |   |

|     | BASE DISPLACEMENT (0, 1, OR 2 WORDS) |        |    |     |           |          |          |              |       |    |      |        |       |        |   |

| Field<br>Instruction  | Definition                 | <b>Field</b><br>BS | <b>Definition</b> Base Register Suppress                         |

|-----------------------|----------------------------|--------------------|------------------------------------------------------------------|

| Register<br>Extension | General Register Number    |                    | 0 = Base Register Added<br>1 = Base Register Suppressed          |

| Register              | Index Register Number      | IS                 | Index Suppress                                                   |

| D/A                   | Index Register Type 0 = Dn |                    | 0 = Evaluate and Add Index Operand<br>1 = Suppress Index Operand |

|                       | 1 = An                     | BD SIZE            | Base Displacement Size                                           |

| W/L                   | Word/Long Word Index Size  |                    | 00 = Reserved                                                    |

|                       | 0 = Sign-Extended Word     |                    | 01 = Null Displacement                                           |

|                       | 1 = Long Word              |                    | 10 = Word Displacement                                           |

| Scale                 | Scale Factor               |                    | 11 = Long-Word Displacement                                      |

|                       | 00 = 1                     | I/IS *             | Index/Indirect Selection                                         |

|                       | 01 = 2                     |                    | Indirect and Indexing Operand                                    |

|                       | 10 = 4                     |                    | Determined in Conjunction with Bit 6,                            |

|                       | 11 = 8                     |                    | Index Suppress                                                   |

<sup>\*</sup>Memory indirect addressing will cause illegal instruction trap; must be = 000 if IS = 1

Figure 3-2 Effective Address Specification Formats

EA modes can be classified as follows:

Data A data addressing EA mode refers to data operands.

Memory A memory addressing EA mode refers to memory operands.

An alterable addressing EA mode refers to writable operands.

Control A control addressing EA mode refers to unsized memory operands.

Categories are sometimes combined, forming new, more restrictive, categories. Two examples are alterable memory or alterable data. The former refers to addressing modes that are both alterable and memory addresses; the latter refers to addressing modes that are both alterable and data addresses. **Table 3-1** shows categories to which each of the EA modes belong.

## 3.5 Programming View of Addressing Modes

Extensions to indexed addressing modes, indirection, and full 32-bit displacements provide additional programming capabilities for the CPU32. The following paragraphs describe addressing techniques and summarize addressing modes from a programming point of view.

**Table 3-1 Effective Addressing Mode Categories**

| Addressing Mode                                           | Code | Register | Data | Memory | Control | Alterable | Syntax                    |

|-----------------------------------------------------------|------|----------|------|--------|---------|-----------|---------------------------|

| Data Register Direct                                      | 000  | reg. no. | Х    | _      | _       | Х         | Dn                        |

| Address Register Direct                                   | 001  | reg. no. | _    | _      |         | Х         | An                        |

| Address Register Indirect                                 | 010  | reg.no.  | Х    | Х      | Х       | Х         | (An)                      |

| Address Register Indirect with Postincrement              | 011  | reg. no. | Х    | Х      | _       | X         | (An) +                    |

| Address Register Indirect with Predecrement               | 100  | reg. no. | Х    | Х      |         | X         | – (An)                    |

| Address Register Indirect with Displacement               | 101  | reg.no.  | Х    | Х      | Х       | X         | (d <sub>16,</sub> An)     |